### THE FRONTIERS COLLECTION

#### THE FRONTIERS COLLECTION

Series Editors:

A.C. Elitzur L. Mersini-Houghton M. Schlosshauer M.P. Silverman R. Vaas H.D. Zeh J. Tuszynski

The books in this collection are devoted to challenging and open problems at the forefront of modern science, including related philosophical debates. In contrast to typical research monographs, however, they strive to present their topics in a manner accessible also to scientifically literate non-specialists wishing to gain insight into the deeper implications and fascinating questions involved. Taken as a whole, the series reflects the need for a fundamental and interdisciplinary approach to modern science. Furthermore, it is intended to encourage active scientists in all areas to ponder over important and perhaps controversial issues beyond their own speciality. Extending from quantum physics and relativity to entropy, consciousness and complex systems – the Frontiers Collection will inspire readers to push back the frontiers of their own knowledge.

For a full list of published titles, please see back of book or springer.com/series 5342

Series home page - springer.com

Bernd Hoefflinger Editor

# **Chips 2020**

A Guide to the Future of Nanoelectronics

Editor

Bernd Hoefflinger

Leonberger Str. 5

71063 Sindelfingen

Germany

Series Editors:

Avshalom C. Elitzur

Bar-Ilan University, Unit of Interdisciplinary Studies, 52900 Ramat-Gan, Israel email: avshalom.elitzur@weizmann.ac.il

Laura Mersini-Houghton

Dept. Physics, University of North Carolina, Chapel Hill, NC 27599-3255, USA

email: mersini@physics.unc.edu

Maximilian A. Schlosshauer

Institute for Quantum Optics and Quantum Information, Austrian Academy of Sciences,

Boltzmanngasse 3, A-1090 Vienna, Austria

email: schlosshauer@nbi.dk

Mark P. Silverman

Trinity College, Dept. Physics, Hartford CT 06106, USA

email: mark.silverman@trincoll.edu

Jack A. Tuszvnski

University of Alberta, Dept. Physics, Edmonton AB T6G 1Z2, Canada

email: jtus@phys.ualberta.ca

Rüdiger Vaas

University of Giessen, Center for Philosophy and Foundations of Science, 35394 Giessen,

Germany

email: ruediger.vaas@t-online.de

H. Dieter Zeh

Gaiberger Straße 38, 69151 Waldhilsbach, Germany

email: zeh@uni-heidelberg.de

ISSN 1612-3018

ISBN 978-3-642-22399-0

e-ISBN 978-3-642-23096-7

DOI 10.1007/978-3-642-23096-7

Springer Heidelberg Dordrecht London New York

Library of Congress Control Number: 2011943001

#### © Springer-Verlag Berlin Heidelberg 2012

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilm or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### **Preface**

On July 30, 1959, Robert Noyce filed his Integrated Circuit patent. Its fiftieth anniversary in 2009 became the origin of this book and its central question: After the unparalleled progress of microchips over half a century, can this story continue, and what will it take to make this happen?

To greet the year 2000, I had written an invited paper "Chips 2020" for the German magazine *Elektronik* (with a strong vote for 3D chip integration), and it looked attractive to check the status at half-time, in 2010. However, the central issue of this book emerged owing to more and more signs of the imminent end of the nano(meter) *roadmap*: The law that halving the transistor size every 18 months would bring automatic performance and market growth is about to end in 2015. When the billions of 10 nm×10 nm transistors packed side-by-side on a chip are hardly useful because of their fundamental statistical variance, we face the most important turning point in the history of microelectronics: Declining growth in markets and services and an energy crisis on top, because, with the chip technology of 2010 and with the present annual doubling of video and TV on the internet, this service alone would require the total worldwide electrical power in 2015.

Chips 2020 explains the background to the 20–10 nm transistor limits in different applications, and it focuses on the new strategy for the sustainable growth of a nanoelectronics ecosystem with a focus on ultra-low energy of all chip functionalities, femtojoule electronics, enabled by 3D integration on-chip and of chip-systems incorporating new architectures as well as new lithography and silicon technologies.

At the critical time of this new fundamental energy orientation, I have been very fortunate that several world leaders with their teams agreed to contribute to this book: Greg Delagi of Texas Instruments, on intelligent mobile companions, the new lead products; Georg Kimmich of ST-Ericsson, on 3D integration for wireless applications; Burn Lin of TSMC, on nanolithography; Jiri Marek and Udo Gomez of Robert Bosch GmbH, on MEMS (micro-electro-mechanical systems) for automotive and consumer applications; Barry Pangrle of Mentor Graphics, on power-efficient design; Peter Roth and colleagues at IBM, on superprocessors; Yiannos Manoli with his team at the University of Freiburg, together with Boris Murmann of Stanford University, on analog—digital interfaces and energy harvesting; Albrecht

vi Preface

Rothermel of the University of Ulm, on retinal implants for blind patients; and Ben Spaanenburg with his co-author at Lund University, on digital neural networks. This book would be unthinkable without their contributions, and, in this critical situation for nanoelectronics, I am even more obliged to them for their involvement in this project.

Despite our broad agenda, we could cover only selected topics, which, we hope, are exemplary for the potential and challenges for 2020 chips.

My sincere thanks go to Claus Ascheron at Springer in Heidelberg, who constantly pursued the idea for this book and who finally convinced me in 2009 to realize it. I thank the team at Springer Science+Business Media for their confidence in this publication and for its professional production. I thank Stefanie Krug for her perfect execution of many of the illustrations and Deborah Marik for her professional editing of the manuscript.

With experience as the first MOS product manager at Siemens and of co-founding a Technical University and establishing several microchip research facilities in the USA and Germany, I have included educational, research, and business aspects of the nanoelectronics ecosystem. I hope that, with this scope, this book will be helpful to all those who have to make decisions associated with future electronics, from students to graduates, educators, and researchers, as well as managers, investors, and policy makers.

Sindelfingen Bernd Hoefflinger

### **Contents**

| 1  | Bernd Hoefflinger                                                                    | . 1 |

|----|--------------------------------------------------------------------------------------|-----|

| 2  | From Microelectronics to Nanoelectronics  Bernd Hoefflinger                          | 13  |

| 3  | The Future of Eight Chip Technologies                                                | 37  |

| 4  | Analog-Digital Interfaces                                                            | 95  |

| 5  | Interconnects, Transmitters, and Receivers Bernd Hoefflinger                         | 131 |

| 6  | Requirements and Markets for Nanoelectronics                                         | 141 |

| 7  | ITRS: The International Technology Roadmap for Semiconductors Bernd Hoefflinger      | 161 |

| 8  | Nanolithography                                                                      | 175 |

| 9  | Power-Efficient Design Challenges  Barry Pangrle                                     | 189 |

| 10 | Superprocessors and Supercomputers  Peter Hans Roth, Christian Jacobi, and Kai Weber | 215 |

viii Contents

| 11   | Towards Terabit Memories  Bernd Hoefflinger                                                                                                                                             | 229 |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

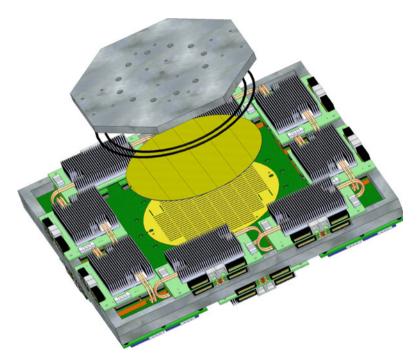

| 12   | 3D Integration for Wireless Multimedia                                                                                                                                                  | 251 |  |  |

| 13   | Technology for the Next-Generation-Mobile User Experience  Greg Delagi                                                                                                                  | 273 |  |  |

| 14   | MEMS (Micro-Electro-Mechanical Systems) for Automotive and Consumer Electronics                                                                                                         | 293 |  |  |

| 15   | Vision Sensors and Cameras  Bernd Hoefflinger                                                                                                                                           | 315 |  |  |

| 16   | Digital Neural Networks for New Media  Lambert Spaanenburg and Suleyman Malki                                                                                                           | 331 |  |  |

| 17   | Retinal Implants for Blind Patients  Albrecht Rothermel                                                                                                                                 | 367 |  |  |

| 18   | Silicon Brains Bernd Hoefflinger                                                                                                                                                        | 383 |  |  |

| 19   | Energy Harvesting and Chip Autonomy Yiannos Manoli, Thorsten Hehn, Daniel Hoffmann, Matthias Kuhl, Niklas Lotze, Dominic Maurath, Christian Moranz, Daniel Rossbach, and Dirk Spreemann | 393 |  |  |

| 20   | The Energy Crisis  Bernd Hoefflinger                                                                                                                                                    | 421 |  |  |

| 21   | The Extreme-Technology Industry Bernd Hoefflinger                                                                                                                                       | 429 |  |  |

| 22   | <b>Education and Research for the Age of Nanoelectronics</b>                                                                                                                            | 439 |  |  |

| 23   | 2020 World with Chips                                                                                                                                                                   | 451 |  |  |

| Ind  | Index                                                                                                                                                                                   |     |  |  |

| Titl | les in this Series                                                                                                                                                                      | 479 |  |  |

#### **Contributors**

**Greg Delagi** Texas Instruments, 12,500 TI Boulevard, MS 8723, Dallas, TX, 75243, USA, t-wright@ti.com

**Dr. Udo-Martin Gómez** Robert Bosch GmbH, Automotive Electronics (AE/NE4), Postfach 1,342, 72703 Reutlingen, Germany, Udo-Martin.Gomez@de. bosch.com

**Thorsten Hehn** IMTEK Microelectronics, University of Freiburg, Georges-Koehler-Allee 102, 79106 Freiburg, Germany

**Prof. Bernd Hoefflinger** Leonberger Strasse 5, 71063 Sindelfingen, Germany, bhoefflinger@t-online.de

**Dr. Daniel Hoffmann** HSG-IMIT, Institute of Micromachining and Information Technology, Wilhelm-Schickard-Strasse 10, 78052 Villingen-Schwenningen, Germany

**Dr. Christian Jacobi** IBM Systems & Technology Group, Technology Development, Schoenaicher Strasse 220, 71032 Boeblingen, Germany, cjacobi@de.ibm.com

**Dr. Matthias Keller** IMTEK Microelectronics, University of Freiburg, Georges-Koehler-Allee 102, 79110 Freiburg, Germany, mkeller@imtek.de

**Georg Kimmich** ST-Ericsson 12, rue Jules Horovitz, B.P. 217, 38019 Grenoble Cedex, France, georg.kimmich@stericsson.com

**Matthias Kuhl** IMTEK Microelectronics, University of Freiburg, Georges-Koehler-Allee 102, 79110 Freiburg, Germany

x Contributors

**Dr. Burn J. Lin** TSMC, 153 Kuang Fu Road, Sec. 1, Lane 89, 1st Fl, Hsinchu, Taiwan, R.O.C. 300, burnlin@tsmc.com

**Niklas Lotze** HSG-IMIT, Institute of Micromachining and Information Technology, Wilhelm-Schickard-Strasse 10, 78052 Villingen-Schwenningen, Germany

**Suleiman Malki** Department of Electrical & Information Technology, Lund University, P.O. Box 118, Lund 2210, Germany

**Prof. Yiannos Manoli** Fritz Huettinger Chair of Microelectronics, University of Freiburg, IMTEK, Georges-Koehler-Allee 102, 79110 Freiburg, Germany, manoli@imtek.de

**Dr. Jiri Marek** Robert Bosch GmbH, Automotive Electronics, Postfach 1,342, 72703 Reutlingen, Germany, Jiri.Marek@de.bosch.com

**Dominic Maurath** IMTEK Microelectronics, University of Freiburg, Georges-Koehler-Allee 102, 79110 Freiburg, Germany, maurath@imtek.de

**Christian Moranz** IMTEK Microelectronics, University of Freiburg, Georges-Koehler-Allee 102, 79110 Freiburg, Germany

**Prof. Boris Murmann** Stanford University, 420 Via Palu Mall, Allen-208, Stanford, CA, 94305-40070, USA, murmann@stanford.edu

**Dr. Barry Pangrle** Mentor Graphics, 1,001 Ridder Park Drive, San Jose, CA, 95131-2314, USA, barry\_pangrle@mentor.com

**Daniel Rossbach** HSG-IMIT, Institute of Micromachining and Information Technology, Wilhelm-Schickard-Strasse 10, 78052 Villingen-Schwenningen, Germany

**Dr. Peter Hans Roth** IBM Systems & Technology Group, Technology Development, Schoenaicher Strasse 220, 71032 Boeblingen, Germany, peharo@de.ibm.com

**Prof. Albrecht Rothermel** University of Ulm, Institute of Microelectronics, Albert-Einstein-Allee 43, 89081 Ulm, Germany, info@albrecht-rothermel.de

**Prof. Lambert Spaanenburg** Dept. of Electrical & Information Technology, Lund University, PO Box 11822100 Lund, Sweden, Lambert.Spaanenburg@eit.lth.se

**Dirk Spreemann** HSG-IMIT, Institute of Micromachining and Information Technology, Wilhelm-Schickard-Strasse 10, 78052 Villingen-Schwenningen, Germany

**Kai Weber** System z Core Verification Lead, IBM Systems & Technology Group, Technology Development, Schoenaicher Strasse 220, 71032 Boeblingen, Germany, Kai.Weber@de.ibm.com

### **Biographies of Authors**

Greg Delagi has been senior vice president and general manager of TI's Wireless Terminals Business since 2007, where he leads TI's worldwide development of semiconductors for mobile phones. Greg Delagi started his career with Texas Instruments in 1984 with the Materials and Controls Business. He later joined TI's Semiconductor Group. Delagi was responsible for several of the company's business units such as DSL, Cable, VoIP and Wireless LAN, creating systems-on-chip solutions. As vice president and manager of TI's Digital Signal Processing (DSP) business, he guided the company to its world leadership with a 62% share of the world market in 2006. He is a graduate of Nichols College in Dudley, MA, where he earned a BSBA in 1984.

**Udo Gómez** has been Director of Engineering since 2006 for Advanced Sensor Concepts at Bosch, Automotive Electronics Division, in Reutlingen, Germany, responsible for MEMS sensor predevelopment activities. He also serves as chief expert for MEMS sensors. From 2003 until 2005, he was responsible for the development of a novel automotive inertial sensor cluster platform for active safety applications. Dr. Gómez studied physics at the University of Stuttgart, Germany. In 1997, he received his Ph.D. from the University of Stuttgart for his work on molecular electronics. In January 1998, he joined the California Institute of Technology as a post-doctoral fellow. In 1999, he started his work at Bosch Corporate Research.

Bernd Hoefflinger started his career as an assistant professor in the Department of Electrical Engineering at Cornell University, Ithaca, NY, USA. Returning to Germany, he served as the first MOS product manager at Siemens, Munich. With that background, he became a co-founder of the University of Dortmund, Germany, and later head of the Electrical Engineering Departments at the University of Minnesota and at Purdue University, IN, USA. In 1985, he became the director of the newly established Institute for Microelectronics Stuttgart (IMS CHIPS), a public contract research and manufacturing institute. In 1993, IMS CHIPS became the world's first ISO 9000 certified research institute. He launched rapid prototyping with electron-beam lithography in 1989. He established the institute as a leader in high-dynamic-range CMOS imagers and video cameras from 1993 onwards. Among the developments in CMOS photosensors was the chip design and manufacturing for the first sub-retinal implants in humans in Europe in 2005. He retired in 2006.

Christian Jacobi received both his M.S. and Ph.D. degrees in computer science from Saarland University, Germany, in 1999 and 2002, respectively. He joined IBM Research and Development in 2002, working on floating-point implementation for various IBM processors. For IBM's System z10 mainframe, he worked on the L1.5 cache unit. From 2007 to 2010, Dr. Jacobi was on international assignment to Poughkeepsie, NY, where he worked on the Load-Store-Unit for the IBM zEnterprise 196 mainframe. Dr. Jacobi is now responsible for the cache design of IBM's mainframe processors, and for future architecture extensions.

Matthias Keller was born in Saarlouis, Germany, in 1976. He received his Diploma degree in electrical engineering from the University of Saarland, Saarbrücken, Germany, in 2003 and a Dr.-Ing. degree (summa cum laude) from the University of Freiburg, Germany, in 2010. From 2003 to 2009, he was a research assistant at the Fritz Huettinger Chair of Microelectronics at the University of Freiburg, Germany, in the field of analog CMOS integrated circuit design with an emphasis on continuous-time delta-sigma A/D converters. In 2009, he was awarded a tenured position as a research associate ("Akademischer Rat"). His research interests are analog integrated circuits based on CMOS technology, in particular delta-sigma A/D converters and patch-clamp readout circuits.

Georg Kimmich is product manager at ST-Ericsson in Grenoble, France. He is responsible for the product definition of digital baseband system-on-chip products within the 3G Multimedia and Platform Division. His focus is on the technology roadmap definition for chip packaging. Georg Kimmich graduated in computer engineering at HFU, Furtwangen, Germany in 1990. He held several design and management positions in the design automation and ASIC design domain with Thomson Multimedia and STMicroelectronics in Germany, France and the US. In 2006, he joined the application processor division of STMicroelectronics, where he was responsible for the system-on-chip development team of the Nomadik application processor family.

**Burn J. Lin** became a vice president at TSMC, Ltd., in 2011. He joined TSMC in 2000 as a senior director. Prior to that, he founded Linnovation, Inc. in 1992. Earlier he held various technical and managerial positions at IBM after joining IBM in 1970. He has been extending the limit of optical lithography for close to four decades. He pioneered many lithography techniques, among them deep-UV lithography starting from 1975, multi-layer resist from 1979, Exposure-Defocus methodology from 1980,  $k_1$  reduction from 1987, attenuated phase-shifting mask from 1991, 193 nm immersion lithography from 2002, and polarization-dependent stray light from 2004. He is currently working on cost-effective optical lithography and multiple-electron-beam mask-less lithography for the 20 nm node and beyond.

Dr. Lin is the editor-in-chief of the *Journal of Micro/nanolithography, MEMS, and MOEMS*, life member of the US National Academy of Engineering, IEEE Life Fellow, and SPIE Fellow. He has received numerous awards, among them the 1st Semi IC Outstanding Achievement Award in 2010, the 2009 IEEE Cledo Brunetti Award, the 2009 Benjamin G. Lammé Meritorious Achievement Medal, and in 2004 the 1st SPIE Frits Zernike award. Throughout his career, he has received numerous TSMC and IBM Awards. He has written one book and three book chapters, published 121 articles, mostly first-authored, and holds 66 US patents.

**Suleyman Malki** received, in October 2008, a Ph.D. degree from the Department of Electrical and Information Technology at Lund University for work on the topic "Reconfigurable and Parallel Computing Structures in Structured Silicon". Before that he received a master's degree in computer science and engineering from Lund University. His research has focused mainly on the implementation and verification of highly intelligent systems on reconfigurable chips (FPGA). Currently he is devoting most of his time to his recent biological and industrial offspring.

**Yiannos Manoli** was born in Famagusta, Cyprus. As a Fulbright scholar, he received a B.A. degree (summa cum laude) in physics and mathematics from Lawrence University in Appleton, WI, in 1978 and a M.S. degree in electrical engineering and computer science from the University of California, Berkeley, in 1980. He obtained a Dr.-Ing. degree in electrical engineering from the University of

Duisburg, Germany, in 1987. From 1980 to 1984, he was a Research Assistant at the University of Dortmund, Germany. In 1985, he joined the newly founded Fraunhofer Institute of Microelectronic Circuits and Systems, Duisburg, Germany, From 1996 to 2001, he held the Chair of Microelectronics with the Department of Electrical Engineering, University of Saarbrücken, Germany. In 2001, he joined the Department of Microsystems Engineering (IMTEK) of the University of Freiburg, Germany, where he established the Chair of Microelectronics. Since 2005, he has additionally served as one of the three directors at the "Institute of Micromachining and Information Technology" (HSG-IMIT) in Villingen-Schwenningen, Germany. He spent sabbaticals with Motorola (now Freescale) in Phoenix, AZ, and with Intel, Santa Clara, CA. Prof. Manoli has received numerous best paper and teaching awards, and he has served on the committees of ISSCC, ESSCIRC, IEDM and ICCD. He was Program Chair (2001) and General Chair (2002) of the IEEE International Conference on Computer Design (ICCD). He is on the Senior Editorial Board of the IEEE Journal on Emerging and Selected Topics in Circuits and Systems and on the Editorial Board of the Journal of Low Power Electronics. He served as guest editor of Transactions on VLSI in 2002 and Journal of Solid-State Circuits in 2011.

Jiri Marek has been Senior Vice President of Engineering Sensors at Bosch, Automotive Electronics Division, since 2003, responsible for the MEMS activities at Bosch. He started his work at Bosch in 1986. From 1990 until 1999, he was responsible for the Sensor Technology Center. In 1999, he became Vice President Engineering of Restraint Systems and Sensors. Dr. Marek studied Electrical Engineering at the University of Stuttgart, Germany, and Stanford University, USA. In 1983, he received his Ph.D. from the University of Stuttgart for his work at the Max Planck Institute Stuttgart on the analysis of grain boundaries in large-grain polycrystalline solar cells. After a post-doctoral fellowship with IBM Research, San José, CA, he was a development engineer with Hewlett-Packard, Optical Communication Division.

Boris Murmann is an Associate Professor in the Department of Electrical Engineering, Stanford University, CA, USA. He received his Dipl.-Ing. (FH) degree in communications engineering from Fachhochschule Dieburg, Germany, in 1994, a M.S. degree in electrical engineering from Santa Clara University, CA, in 1999, and his Ph.D. degree in electrical engineering from the University of California, Berkeley, in 2003. From 1994 to 1997, he was with Neutron Mikrolektronik GmbH, Hanau, Germany, where he developed low-power and smart-power ASICs in automotive CMOS technology. Dr. Murmann's research interests are in the area of mixed-signal integrated circuit design, with special emphasis on data converters and sensor interfaces. In 2008, he was a co-recipient of the Best Student Paper Award at the VLSI Circuit Symposium and the recipient of the Best Invited Paper Award at the Custom Integrated Circuits Conference (CICC), In 2009, he received the Agilent Early Career Professor Award. Dr. Murmann is a member of the International Solid-State-Circuits Conference (ISSCC) program committee, an associate editor of the IEEE Journal of Solid-State Circuits, and a Distinguished Lecturer of the IEEE Solid-State Circuits Society.

**Barry Pangrle** is a Solutions Architect for Low Power in the Engineered Solutions Group at Mentor Graphics Corporation. He has a B.S. in computer engineering and a Ph.D. in computer science, both from the University of Illinois at Urbana-Champaign. He has been a faculty member at University of California, Santa Barbara and Penn State University, where he taught courses in computer

architecture and VLSI design while performing research in high-level design automation. Barry has previously worked at Synopsys, initially on high-level design tools and then later as an R&D director for power optimization and analysis tools. He was the Director of Design Methodology for a fabless start-up company and has also worked at a couple of privately held EDA companies, where he focused on design automation tools for low power/energy designs. He has published over 25 reviewed works in high level design automation and low power design and served as a Technical Program Co-chair for the 2008 ACM/IEEE International Symposium on Low Power Electronics Design (ISLPED). He was also actively involved with the technical program committees for ISLPED and DAC for 2009 and was one of the General Co-Chairs for ISLPED 2010.

**Peter H. Roth** received his Dipl.-Ing. degree in electrical engineering and his Dr.-Ing. degree from the University of Stuttgart, Germany, in 1979 and 1985, respectively. In 1985, he joined the IBM Germany Research and Development Lab in Boeblingen, starting in the department of VLSI logic-chip development. Since 1987 he has been leading the VLSI test and characterization team of the Boeblingen lab. Later, Dr. Roth led several development projects in the area of IBM's Mainframe and Power microprocessors. He also was heavily involved in the development of gaming products such as the Cell processor for the Sony PlayStation. Today, Dr. Roth is responsible for the hardware strategy for the IBM Germany Research and Development Laboratory.

Albrecht Rothermel received his Dipl.-Ing. degree in electrical engineering from the University of Dortmund, and his Dr.-Ing. (Ph.D.) degree from the University of Duisburg, both Germany, in 1984 and 1989, respectively. From 1985 to 1989, he was with the Fraunhofer Institute of Microelectronic Circuits and Systems, Duisburg, Germany. From 1990 to 1993, he was with Thomson Consumer Electronics (Thomson Multimedia), Corporate Research, Villingen-Schwenningen, Germany. As manager of the IC design laboratory, he was involved in analog and mixed circuit design for audio and video. Since 1994, he has been with the Institute of Microelectronics, University of Ulm, Germany, as a Professor of Electrical Engineering. Dr. Rothermel was a guest scientist at Thomson Multimedia in Indianapolis, USA (1997), at the Edith-Cowan University in Perth, Western Australia (2003), and at the Shandong University in Jinan, P.R. China (2006). He has published more than 100 papers, book chapters, and patents and received numerous best-paper awards. He was an Associate Editor of the IEEE Journal of Solid-State Circuits, and he is a member of the program committees of ISSCC, ESSCIRC, and ICCE. He is a senior member and distinguished lecturer of the IEEE.

**Lambert Spaanenburg** received his master's degree in electrical engineering from Delft University and his doctorate in technical sciences from Twente University, both in The Netherlands. He started his academic journey at Twente University in the field of VLSI design, eventually serving as CTO of ICN, the commercial spin-off of the ESPRIT Nelsis project. At IMS in Stuttgart, he co-created the neural

control for the Daimler OSCAR 1992 prototype, currently an upcoming standard for car safety measures. He became a full professor at the University of Groningen, The Netherlands. Further research of his group in neural image processing led in 2002 to Dacolian, which held a 60% market share for license-plate recognition before it merged into Q-Free ASA. Overall, Dr. Spaanenburg has produced more than 200 conference papers, 20 reviewed journal articles and seven books or chapters. He has served annually on several program committees and journal boards. He has been involved in many technology transfer projects, including eight university spin-offs. Currently a guest at Lund University, he is exploiting further research on embedded sensory networks with cloud connectivity under the umbrella of RaviteQ AB in Sweden.

Kai Weber received his Dipl.-Ing.(BA) in information technology from the University of Collaborative Education, Stuttgart, and a bachelor degree in computer science from the Open University, UK, in 2003. He joined IBM Research and Development in 2003, working on formal verification of floating-point units and leading the floating-point unit verification teams for IBM's POWER6 and z10 processors. Mr. Weber was the processor verification team leader for the IBM zEnterprise 196 mainframe and continues in this role for future generations of IBM System z processors. In addition Mr. Weber is participating in two joint research projects with the University of Tuebingen and Saarland University evaluating hybrid systems and business analytic workloads.

### **Acronyms and Abbreviations**

AAEE American Association for Engineering Education

AC Alternating current

ACM Association for Computing Machinery

ADC Analog-digital converter

AI Artificial intelligence

ALE Atomic-layer epitaxy

ALU Arithmetic logic unit

AMD Age-related macula degeneration

ANN Artificial neural network

AP Action potential APS Active-pixel sensor

APSM Advanced porous silicon membrane

AQL Acceptable quality level

ARPA Advanced Research Projects Agency

ASIC Application-specific integrated circuit

ASIP Algorithm-specific integrated processor

ASP Application-specific processor

ASS Application-specific system

AVG Available voltage gain

AVS Adaptive voltage scaling

BAN Body-area network

BAW Bulk acoustic wave

BEOL Back-end of line

BI Backside illumination BiCMOS Bipolar CMOS

**BIST**

BMI Brain-machine interface BST Boundary-scan test

C4 Controlled-collapse chip connect

Built-in self-test

CAD Computer-aided design

CAM Content-addressable memory

CARE Concerted Action for Robotics in Europe

CAT Computer-aided test

CCD Charge-coupled device

CDMA Code-division multiple access

CE Continuing education

CFC Chip-integrated fuel cell

CIFB Cascade of integrators in feedback

CIFF Cascade of integrators in feed-forward

CIS Charge-integration sensor

CISC Complex-instruction-set computer

CMOS Complementary metal—oxide—semiconductor

CNN Cellular neural network

CNT Carbon nanotube

COO Cost of ownership

CORDIC Coordinate rotation digital computer

CPU Central processing unit

CSF Contrast-sensitivity function

CT-CNN Continuous-time CNN

DA Design automation

DAC Design-Automation Conference

DAC Digital-analog converter

DARPA Defense Advanced Research Projects Agency

DBB Digital baseband

dBm Power on a log scale relative to 1 mW

DC Direct current

DCF Digital cancelation filter

DDR2 Dual data rate RAM

DEM Dynamic element matching

DFT Design for test

DIBL Drain-induced barrier lowering

DIGILOG Digital logarithmic

DLP Digital light processing

DMA Direct memory access

DN Digital number

DNN Digital neural network

DPG Digital pattern generator

DPT Double-patterning technology liquid-immersion lithography

DRAM Dynamic random-access memory

DRIE Deep reactive-ion etching

DSP Digital signal processor

DT-CNN Discrete-time CNN

DTL Diode-transistor logic

D-TLB Data-cache translation lookaside buffer DVFS Dynamic voltage and frequency scaling

EBL Electron-beam lithography

ECC Error-correcting code

ECG Electrocardiogram

ECL Emitter-coupled logic

EDA Electronic design automation EEG Electroencephalography

EITO European Information Technology Organization

**ELO** Epitaxial lateral overgrowth Epitaxial-layer transfer **ELTRAN** Electromagnetic interference **EMI ENOB** Effective number of bits **EOT** Equivalent oxide thickness **ERC Engineering Research Center** Emerging research devices **ERD** Emerging research materials **ERM** Electrostatic discharge **ESD**

ESD Electrostatic discharge

ESL Electronic-system level

ESP Electronic safety package

ESP Electronic Stability Program

ESPRIT European Strategic Programme for Research in Information

Technology

EUV Extreme ultraviolet

EWS Electrical wafer sort

FACETS Fast Analog Computing with Emergent Transient States

FC Fuel cell

FD SOI Fully depleted silicon-on-inulator

FED Future Electron Devices

FEOL Front-end of line

FeRAM Ferroelectric random-access memory

FET Field-effect transistor

$F^2$  Square of minimum feature size

FFT Fast Fourier transform FIFO First-in-first-out

FIPOS Full isolation by porous silicon

FIR Finite impulse response

FIT Failure in 10<sup>7</sup> h

FLOP Floating-point operation

FMEA Failure mode and effect analysis

FOM Figure-of-merit

FPAA Field-programmable analog array FPGA Field-programmable gate array

fps frames per second

FR Floating-point register

FSM Finite-state machine

FSR Full signal range

GAPU Global analogic programming unit

GBP Gain-bandwidth product

GFC Glucose fuel cell

GIPS Giga instructions per second

GOPS Giga operations per second

GPS Global Positioning System

GPU Graphics processing unit

GR General-purpose register

GSM Global System for Mobile Communication

HAC Hardware accelerator

HD High definition *or* high density

HDL Hardware description language

HDR High dynamic range

HDRC High-Dynamic-Range CMOS

HDTV High-definition television

HIPERLOGIC High-performance logic

HKMG High-k metal gate

HLS High-level synthesis

HVM High-volume manufacturing IBL Ion-beam lithography IC Integrated circuit

ICT Information and communication technology IEDM International Electron Devices Meeting

IEEE Institute of Electrical and Electronics Engineers

IFFT Inverse fast Fourier transform I<sup>2</sup>L Integrated injection logic

IO Input-output

IOMMU I/O memory mapping unit IP-core Intellectual property core

IS Instruction set

ISO International Organization for Standardization ISSCC International Solid-State Circuits Conference

IT Information technology

I-TLB Instruction-cache translation lookaside buffer

ITRS International Technology Roadmap for Semiconductors

ITS Intelligent transportation systems

JEDEC Joint Electron Device Engineering Council JESSI Joint European Submicron Silicon Initiative

JIT compiler Just-in-time compiler

JND Joust noticeable difference

JPEG Joint Photography Expert Group

KGD Known-good die LCA Life-cycle analysis

LDO Low-voltage dropout regulator

LOG Localized epitaxial overgrowth

LPC Linear predictive coding

LPDDR Low-power DDR

LSB Least significant bit

LSI Large-scale integration

LTE Long-term evolution

LUT Look-up table

LVDL Low-voltage differential logic

MASH Multi-stage noise shaping

MBE Molecular-beam epitaxy

MCC Manchester carry chain

MCM Multi-chip module

MCU Multi-core processing units

MEBL Multiple-electron-beam lithography

MEMS Micro-electro-mechanical system

MIPS Mega instructions per second

MITI Ministry of International Trade and Industry (Japan)

MLC Multi-level per cell

MMI Man-machine interface

MMI Machine-machine interface

MOPS Million operations per second

MOS Metal-oxide-semiconductor

MOSIS MOS IC implementation system

MPEG Motion-Picture Expert Group

MPU Microprocessor unit

MRAM Magnetic random-access memory

NA Numerical aperture

NGL Next-generation lithography

NHTSA National Highway Traffic Safety Administration

NIR Near infrared NM Noise margin

NMOS Negative channel-charge MOS

NoC Network on chip

NTF Noise transfer function

NV Nonvolatile

OCT Optical-coherence tomography

ODM Original-device manufacturer

OECD Organisation for Economic Co-operation and Development

OECF Optoelectronic conversion function

OFDM Orthogonal frequency-division multiplexing

OpenCL Open Compute Language – Standard established by the Khronos

Group for platform independent description of highly parallel

computations

ORTC Overall roadmap technology characteristics

**PCM**

OSAT Out-sourced assembly and test

OSCI Open SystemC Initiative

OSR Oversampling ratio

PAE Power-added efficiency

PC Personal computer

PCB Printed-circuit board

PCS Personal Communications Service

PDN Power distribution network

PD SOI partially depleted silicon-on-inulator

Phase-change memory

PE Processing element

PEM Polymer electrolyte membrane

PLL Phase-locked loop

PMOS Positive channel-charge MOS

PMU Power management unit

POP Package-on-package

PPA Power, performance, and area

ppm Parts per million

PVDF Polyvinylidenefluoride

PZT Lead zirconate titanate

QCIF Quarter common intermediate format

QMS Quality-management system

QXGA Quad extended graphics array

RAM Random-access memory

R&D Research and development

REBL Reflective electron-beam lithography

RET Resolution-enhancement technique

RF Radio frequency

RFID Radio frequency identification

RISC Reduced-instruction-set computer

ROI Region of interest

ROM Read-only memory

ROW Rest-of-world

RP Retinitis pigmentosa

RRAM Resistive random-access memory

RTL Register-transfer level

Rx Receive

SAR Successive approximation register SBT Strontium bismuth tantalite

SC Switch capacitor

SD Standard definition

SDR Single data rate

SECE Synchronous electric charge extraction

SEG Selective epitaxial growth

SET Single-electron transistor

SIA Semiconductor industry association SIMOX Silicon isolation by implanting oxygen

$SiO_2$  Silicon dioxide SLD System-level design

SMASH Sturdy multi-stage noise shaping

SMP Symmetric multi-processing

SMT Simultaneous multithreading

SNDR Signal-to-noise-and-distortion ratio

SNM Static noise margin SNR Signal-to-noise ratio SNT Silicon nanotube

SO Switch operational amplifier

SOC System-on-chip SOI Silicon-on-insulator

SPAD Single-photon avalanche diode

SPI Serial peripheral interface

SQNR Signal-to-quantization-noise ratio

SRAM Static random-access memory

SRC Semiconductor Research Corporation

STF Signal transfer function STL Subthreshold leakage STT Spin-torque transfer

SyNAPSE Systems of Neuromorphic Adaptive Plastic Scalable Electronics

TAM Total available market

TFC Thin-film-on-CMOS

TLM Transfer-level modeling

TOPS Tera operations per second

TQM Total quality management

TSV Through-silicon via

TTL Transistor-transistor logic

Tx Transmit

UGBW Unity-gain bandwidth

UL Underwriters Laboratories

ULP Ultralow power

UM Universal model (CNN)

UMTS Universal Mobile Telecommunications System

VCO Voltage-controlled oscillator

VDE Verband Deutscher Elektrotechniker

VDI Verband Deutscher Ingenieure

VDC Vehicle dynamics control

VDS Vehicle dynamics system

VGA Video Graphics Array

VHDL VLSI (originally VHSIC) hardware description language

VHSIC Very-high-speed integrated circuit

VLSI Very-large-scale integration VRD Virtual retinal display VSoC Vision system on chip

wph Wafers per hour

WSI Wafer-scale integration

WSTS World Semiconductor Trade Statistics

XML Extensible Markup Language

Chapter 1

**Introduction: Towards Sustainable 2020**

**Nanoelectronics**

**Bernd Hoefflinger**

**Abstract** Faced with the immanent end of the nanometer roadmap at 10 nm, and with an electronics energy crisis, we have to engineer the largest strategy change in the 50-years history of microelectronics, renamed to nanoelectronics in 2000 with the first chips containing 100-nm transistors.

Accepting the 10 nm-limit, the new strategy for the future growth of chip functionalities and markets has to deliver, within a decade, another  $1,000\times$  improvement in the energy per processing operation as well as in the energy per bit of memory and of communication. As a team from industry and from research, we present expectations, requirements and possible solutions for this challenging energy scenario of femto- and atto-Joule electronics.

The introduction outlines the book's structure, which aims to describe the innovation eco-system needed for optimum-energy, sustainable nanoelectronics. For the benefit of the reader, chapters are grouped together into interest areas like transistors and circuits, technology, products and markets, radical innovations, as well as business and policy issues.

#### 1.1 From Nanoelectronics to Femtoelectronics

In the year 2000, the first microchips were produced with gate lengths <100 nm, and microelectronics received the new label *nanoelectronics*. The drive in the industry along the *nano-roadmap* towards shorter transistors continued in order to build faster processors and to pack more memory bits on each chip. At the same time, the research community had widespread programs running on

1

B. Hoefflinger (⋈)

Leonberger Strasse 5, 71063 Sindelfingen, Germany

e-mail: bhoefflinger@t-online.de

2 B. Hoefflinger

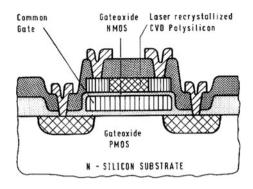

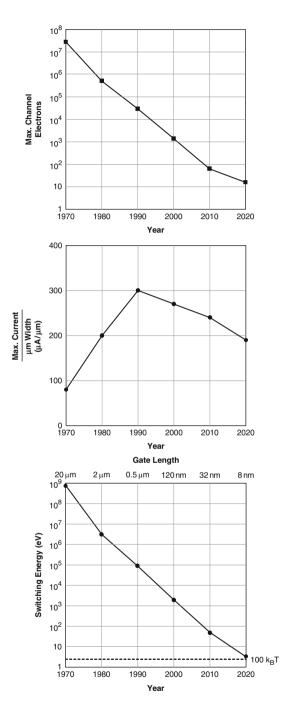

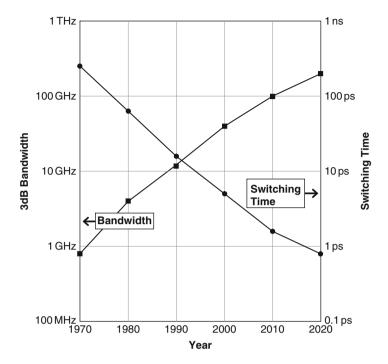

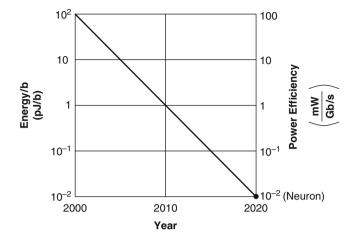

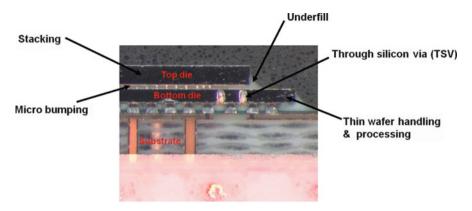

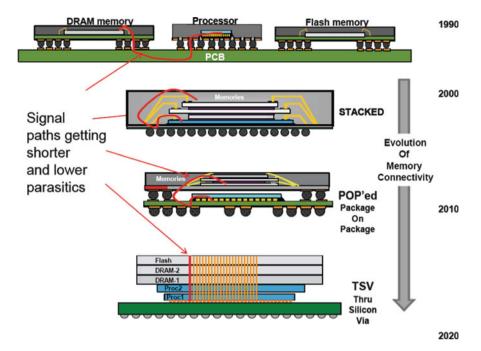

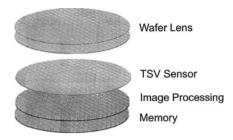

quantum—nanometer-scale phenomena with considerable optimism for near-term practical success. By the year 2010, the planned 32 nm milestone (node) had been reached, including most of the expected chip specifications, but with a twist since 2005: the 3D integration of many thin chips on top of each other, connected through TSVs (through-silicon vias), to enhance the progress on the roadmap. But the year 2010 was also marked by the rapidly growing consensus that the *end of the roadmap is near* at 15 nm (2016) or 10 nm (2018?) at best, and that *none of the new quantum-nano devices will have any economic impact before 2025–2030*. This poses the serious question: Will the progression of chips come to a standstill, and with it the world's driving technology (information and communication)? The answer is: Not necessarily, if we accept the nanometer-limit and, at the same time, exchange the nanometer priority for a femtojoule priority: *Energy per function*, often called the *power efficiency*, *is the new yardstick*.

Between 2010 and 2020, the energy per chip function, such as processing, memory, or communication, has to be reduced by a factor of 1,000 if the nanoelectronics market is going to have enough to offer to six billion potential global customers. Remarkably, many of these chip functions run at picojoule (pJ) levels in 2010. The challenge is now to achieve femtojoule (fJ) levels. Therefore we set our focus on moving from *nano*(meter) *to femto*(joule) *electronics*.

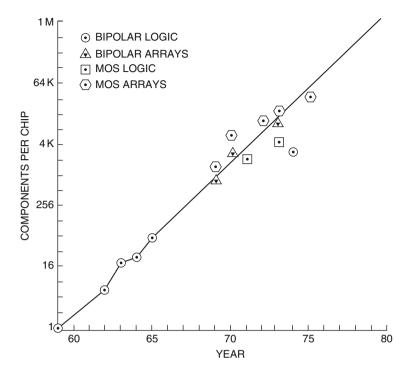

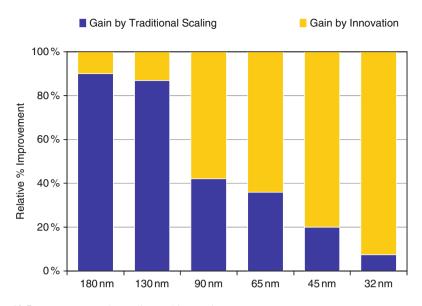

The task is challenging indeed, because the nanometer roadmap only offers a final contribution of threefold at best, which may enter as 3=9 in an energy figure-of-merit (FOM), leaving us with another factor of >100 in needed improvements within a decade. One approach to identifying a future strategy is to consider how the remarkable advances in the 100 years of electronics and, particularly, in the past 50 years of integrated circuits were achieved and which repertory of R&D results of the past 30 years could be put to the test in product developments of the present decade. This is the theme of Chap. 2, "From Microelectronics to Nanoelectronics".

Our path to the 2020 goals will point out critical electronic functions, which are most challenging and intriguing, since we reach and go below the energy per operation in the synapses of natural brains: The typical energy per operation of a neuron's synapse is 10 fJ.

We pose five fundamental questions in this book, and we give answers, all of which point out tough energy requirements on future nanochips so that we conclude: Sustainable nanoelectronics has to be femto(joule) electronics.

Here are the five questions:

- Why do we hit the end of the nano-roadmap?

- Which femtoelectronic solutions can we find for critical functions?

- What are the requirements for new chip products and how can we meet them?

- Which radical femtoelectronic solutions should we seek for intelligent computing?

- What are the challenges for the femtoelectronics ecosystem of education, research, and business?

- How does the 2020 world benefit from femtoelectronic chips?

#### 1.2 Why Do We Hit the End of the Nano-roadmap?

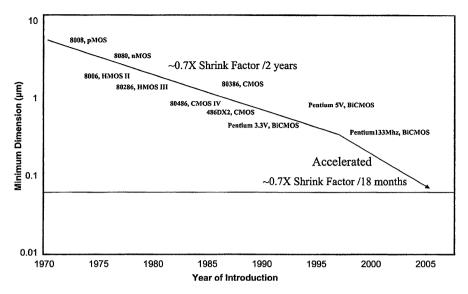

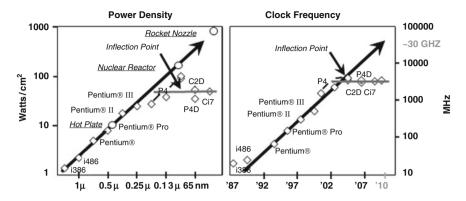

Because microelectronics has advanced so successfully over 50 years with a linear strategy of scaling down transistor sizes, it comes as a surprise that this mode of progression will hit its limits by 2015. We deal with these problems in Chaps. 3 (10 nm transistors), 7 (ITRS, the nano-roadmap), and 8 (nanolithography).

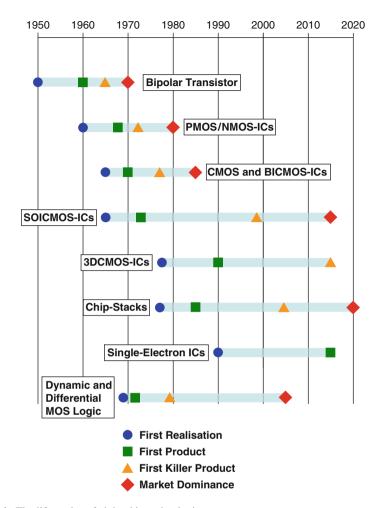

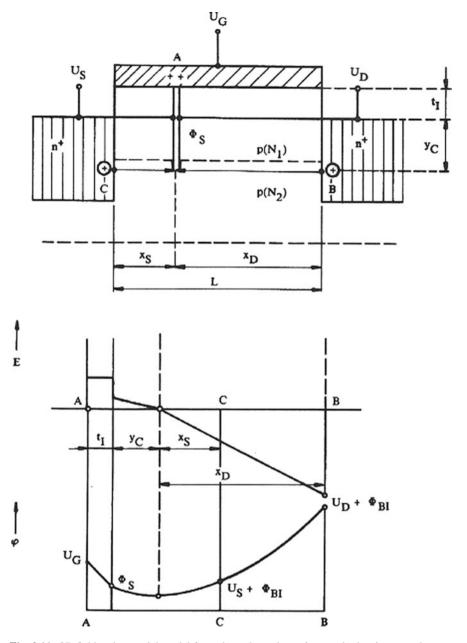

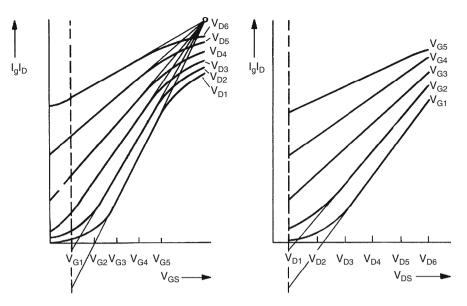

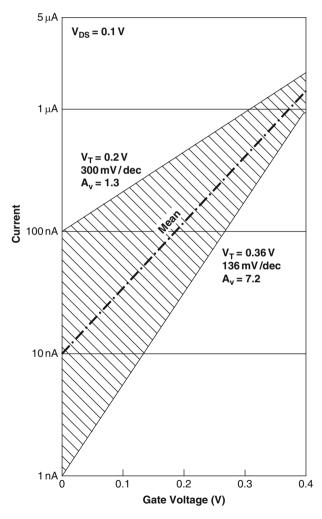

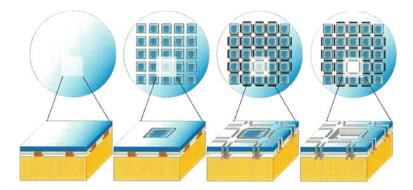

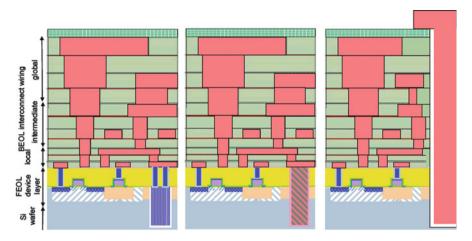

In Chap. 3, we evaluate the future of eight chip technologies, revealing that their development towards a fruitful future took between 25 and more than 35 years, an example being the present emphasis on the 3D integration of chips, which was taken on as a major research topic 30 years ago, only to be put aside in the late 1980s because the 2D scaling strategy did the job well and less *disruptively*. Transistors with gate lengths of <10 nm on the scaling roadmap were built in the lab and published before 2000. Why are their fundamental problems being considered only now? In Sect. 3.2, we identify two fundamental problems, which are present no matter how precisely we can process these 10 nm transistors:

1. The atomic variance (only ~5 doping atoms in the channel) makes the spread of transistor thresholds larger than the allowed supply voltage, so not all of them can be turned on or off.

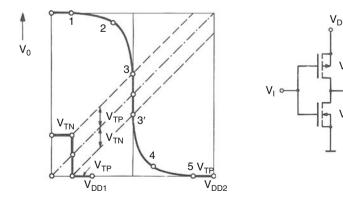

**Fig. 1.1** Minimum supply voltage and switching energy of a CMOS inverter as a function of gate length for an equivalent gate-oxide thickness (EOT) of 1 nm

B. Hoefflinger

2. The available voltage gain (because of drain-induced barrier lowering) becomes <1, and without amplification, circuits lose their signals in noise (at least in all electronics operating in natural environments).

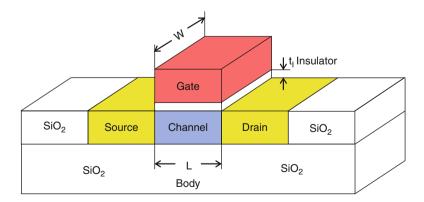

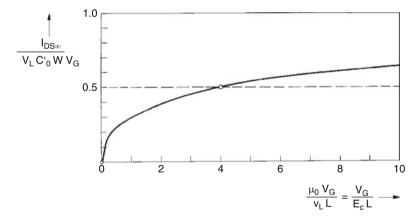

Because of these fundamental limits, we actually find that the most important basic amplifier in modern chip electronics, the CMOS (complementary metal–oxide–semicondiuctor) inverter, has its minimum energy per operation at a gate length of 20 nm (Fig. 1.1), because, moving towards 10 nm, we have to raise the supply voltage in order to compensate for the facts listed above. Nevertheless, the switching energy of this fundamental amplifier is just  $5 \text{ eV} = 10^{-18} \text{ J}$ , which means that we have to move just 25 electrons through a potential difference of 200 mV.

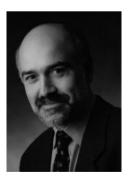

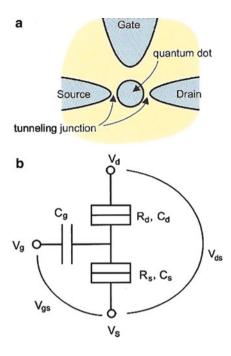

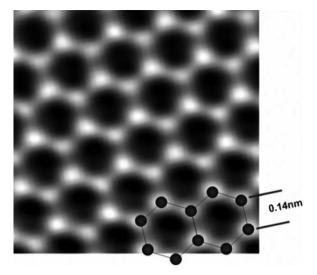

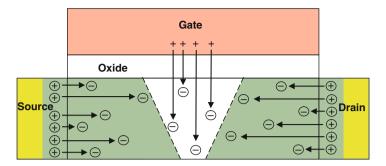

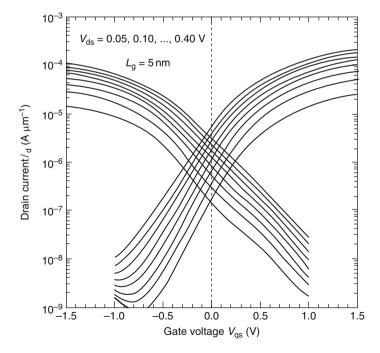

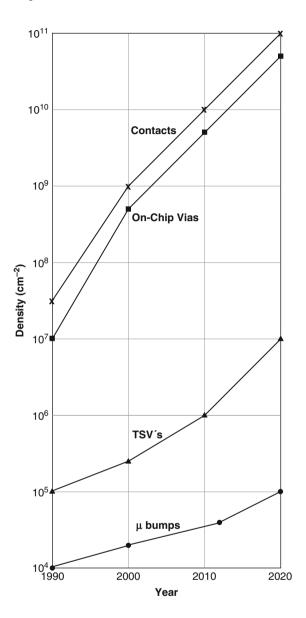

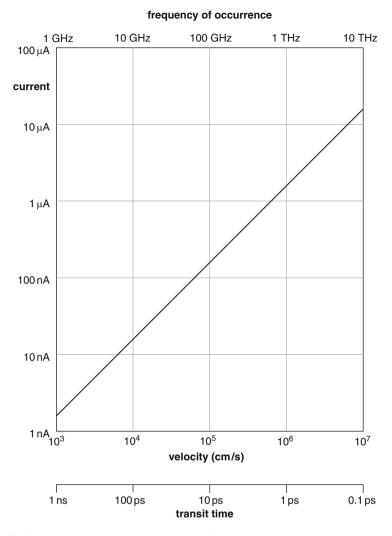

A 10 nm transistor and, for that matter, even a 20 nm transistor, performs this by moving just one electron at a time through the channel at speeds (Fig. 1.2) depending on the instantaneous voltages. That is, practically *all minimum transistors with gate lengths* <20 nm *are single-electron transistors*. We present these fundamental details at the outset of this book in order to show that, at the end of the nanoroadmap, we are putting (at least digital) *information on single electrons*.

Our emphasis when discussing the International Technology Roadmap for Semiconductors (ITRS) in Chap. 7 is the projection for many of the other components

**Fig. 1.2** Current carried by a single electron at a given velocity over a 10 nm distance

on nanochips, such as capacitors and multilevel interconnects, which are important in an assessment of the processing, memory, and communication functions on a chip.

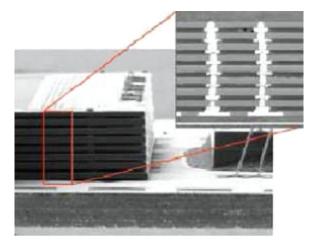

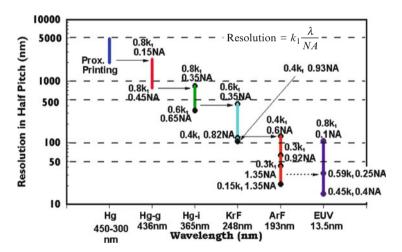

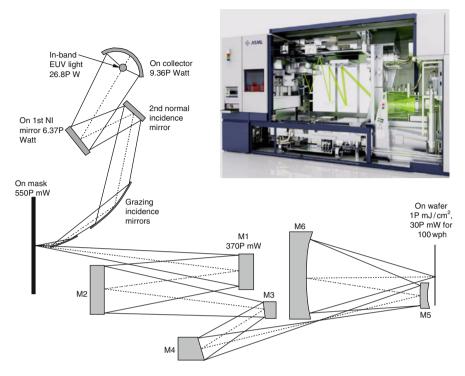

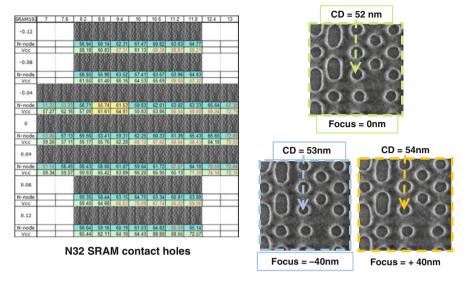

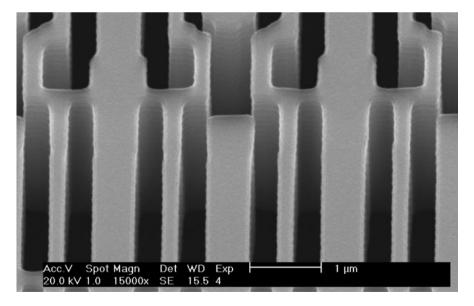

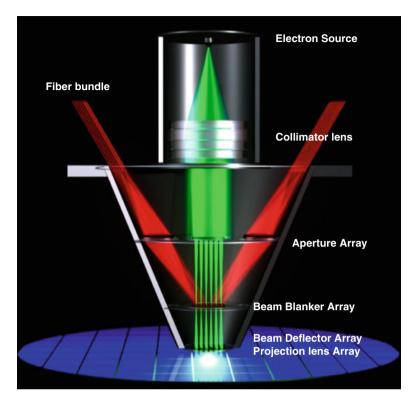

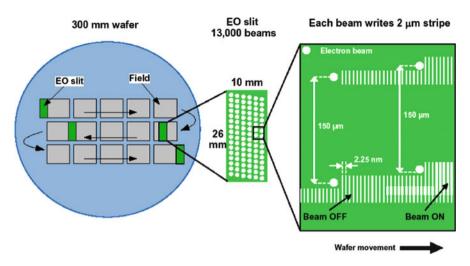

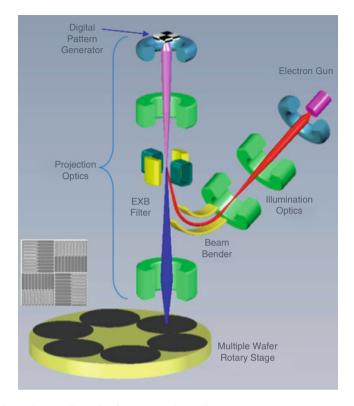

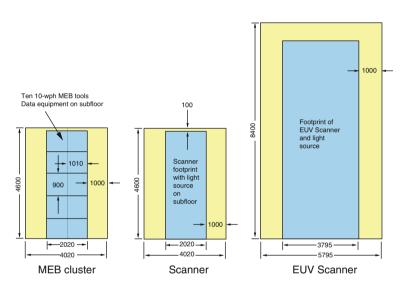

Any of the aggressive projections for down-sizing the features on future chips assume that we can image these features onto the Si wafers, and everyone agrees that nanolithography is the absolute key technology in realizing these incredibly complex structures effectively for many successive layers per wafer and millions of wafers per year. Burn Lin, as vice president of lithography at the world's largest contract manufacturer of wafers, TSMC, recognized as one of the three semiconductor companies at the forefront of technology, addresses both physical and economic issues in Chap. 8. He analyzes the two major contending techniques, EUV (extreme ultraviolet) and MEB (multiple-electron-beam direct write), and he tells us that EUV systems impose extreme requirements on the primary laser source, on the precision of mirrors and masks, and that the overall energy efficiency from plug to wafer is so low that the necessary primary electrical power might be bigger than the total power available for a gigafab (giant semiconductor fabrication plant). On the other hand, an e-beam system, attractive because it is maskless, would need 130,000 parallel, steered beams in order to be competitive, and such a system has not been built as of 2010 owing to a lack of product development. These enormous problems are a third, practical reason besides the fundamental ones listed above for a 10 nm limit on chip features.

## 1.3 Which Femtoelectronic Solutions Can We Find for Critical Functions?

Regarding the question of femtoelectronic solutions, we take the standard position that innovations in technology drive progress (technology push), but we focus this fundamental force on the energy question, combined with operating speed and chip area (footprint/function), in order to meet the great expectations made of future chips. The topics covered and the chapters in which they can be found are listed in Table 1.1.

| Table  | 1.1   | Femtoelectronic |

|--------|-------|-----------------|

| topics | in th | is book         |

| Topic                               | Chapter or section |

|-------------------------------------|--------------------|

| Logic and computing                 | 3, 10              |

| Analog/digital interfaces           | 4                  |

| Interconnects and transceivers      | 5                  |

| Memories                            | 11                 |

| 3D integration                      | 3.5, 12            |

| MEMS sensors                        | 13                 |

| Vision sensors                      | 14                 |

| Retinal implants                    | 17                 |

| Power-efficient design              | 9                  |

| Energy harvesting and chip autonomy | 19                 |

6 B. Hoefflinger

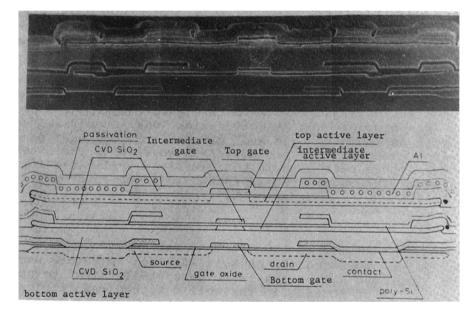

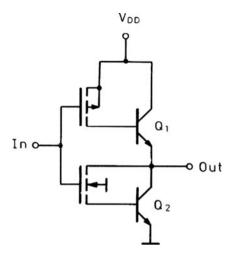

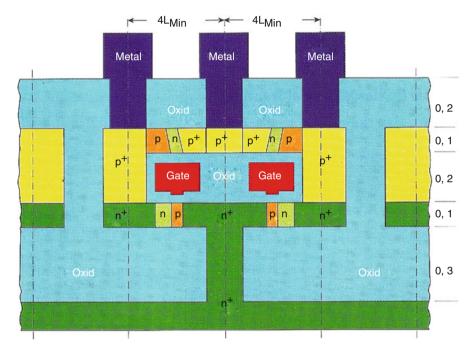

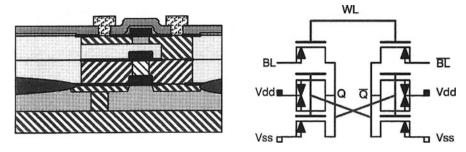

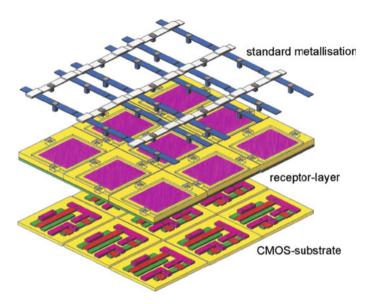

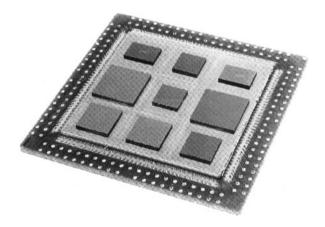

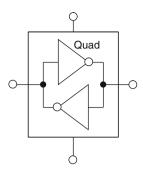

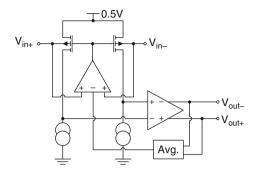

Fig. 1.3 The cross-coupled inverter pair (quad) as a differential signal regenerator, the fundamental building block of ultra-low-voltage digital femtoelectronics

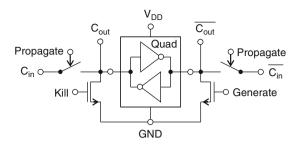

We start out with digital logic in Sect. 3.3, with the conclusion from the preceding section that the variance of 10 nm transistors forces the application of a new type of robust regenerator, the cross-coupled inverter pair, offering a differential, high-speed, full-swing regenerator with minimum dynamic energy. This block of four properly connected transistors (two NMOS and two PMOS) becomes the fundamental circuit unit to be optimized regarding chip footprint and process complexity, presented as a device-level 3D-integrated process in Sects. 3.4 and 3.5. The message here is that, in 10 nm CMOS, the target of making a transistor falls short of the necessary fundamental building block, which is the four-transistor cross-coupled inverter pair with minimum footprint, interconnects, and process steps (Fig. 1.3).

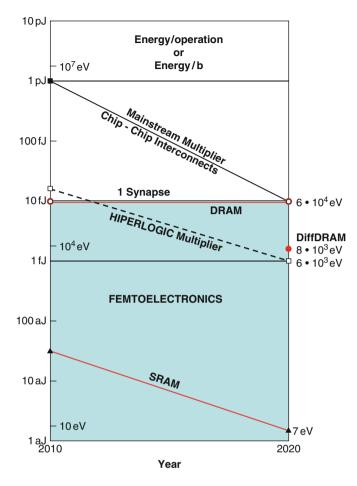

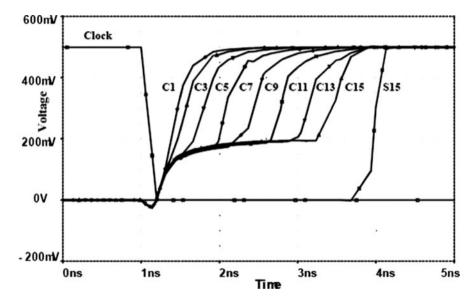

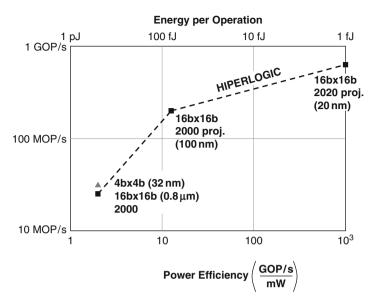

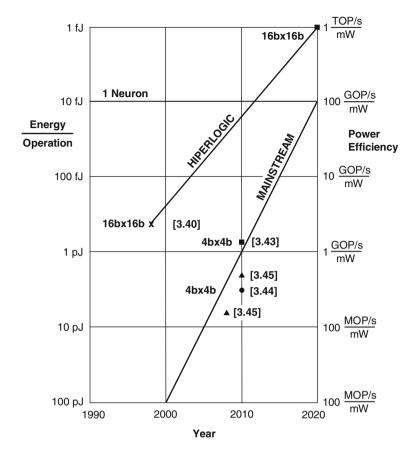

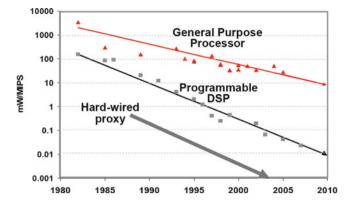

Out of the multitude of applications of the differential regenerator in digital logic, we select the toughest component, the high-speed, minimum-energy, and minimum-footprint multiplier, the largest macro in arithmetic and, especially, in all signal-processing units (images and video). As an example of possible development directions, we describe the HIPERLOGIC multiplier in Sect. 3.6, which has the potential to perform 600 M 16  $\times$  16 bit multiplications with a power-efficiency of one TOps  $mW^{-1}=1$  fJ, which would exceed the 2010 state-of-the-art by a factor of 1,000 (Fig. 1.4).

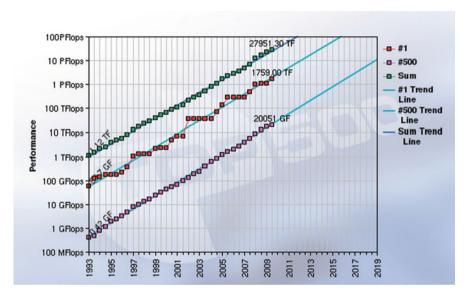

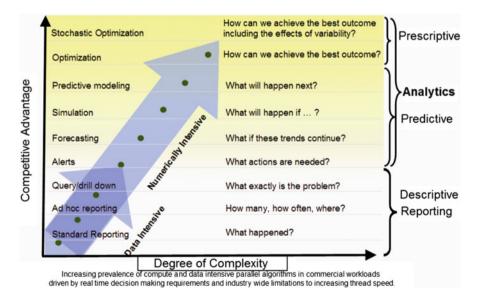

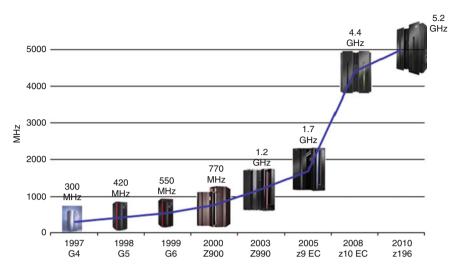

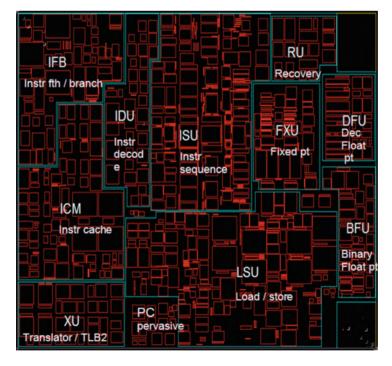

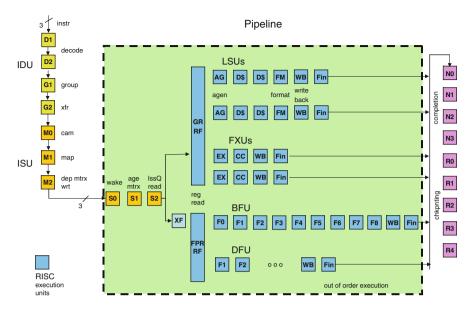

On the higher levels of digital chip functionality, high-performance processors and their future are described by Peter Roth, Christian Jacobi, and Kai Weber of IBM in Chap. 10. Owing to the clock speed limits of <10 GHz towards the end of the nano-roadmap, multicore processors have become a must, and they discuss the associated challenges for operating systems and application development, needing new levels of hardware–software co-design.

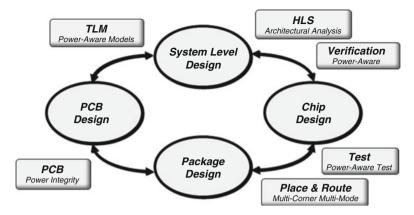

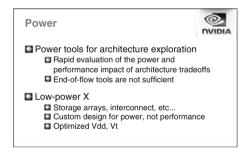

This complex design scenario is analyzed systematically by Barry Pangrle of Mentor Graphics in Chap. 9, with a focus on power efficiency on all levels: system, chip, process technology, test, and packaging. He comes to the conclusion that "it won't be the technology that's the limit but the cost of implementation."

Processors are the much-quoted hearts of advanced integrated chips, but much more functionality is integrated today, namely true *systems-on-a chip* (SOCs). These SOCs incorporate

- Sensors, which sense the environment and mostly produce analog output signals;

- Analog-digital interfaces converting analog sensor or receiver outputs to digital signals for processing;

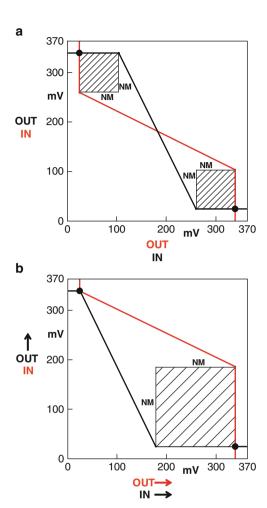

Fig. 1.4 The power-efficiency of digital multipliers and high-speed memory cells advancing to femtojoule and attojoule levels

- Receivers, which receive radio signals or signals on wires as well as optical fibers;

- Transmitters, which send output signals on lines or into space;

- High-speed interconnects on-chip or chip-to-chip;

- Memories, which store digital data and instructions for processing these;

- Energy sources on-chip to produce or/and harvest a part or all of the chip energy necessary for its operation;

- 3D integration as the key technology to merge these functionalities.

The state-of-the-art and the future of the highly sophisticated disciplines treating these specialties are presented in dedicated chapters.

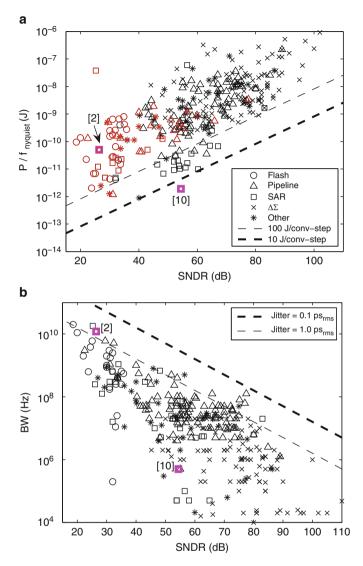

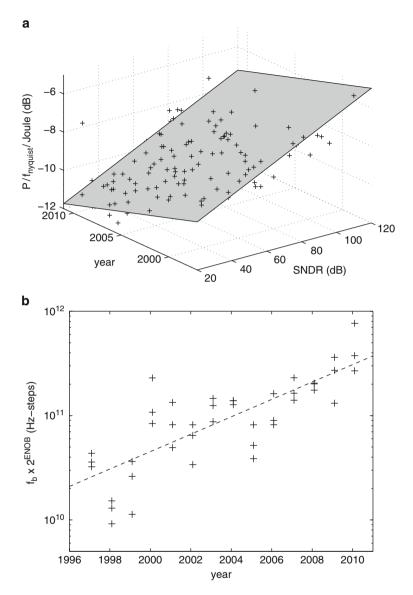

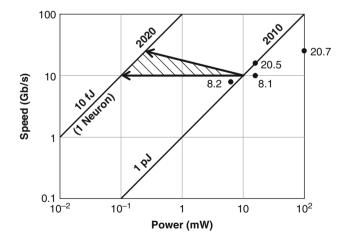

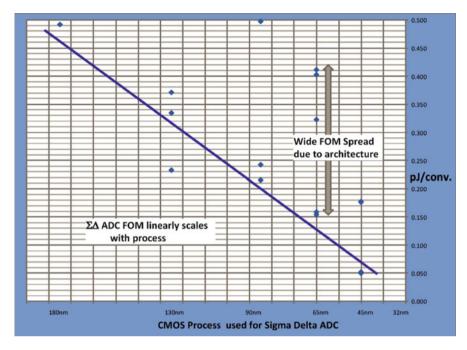

Boris Murmann of Stanford University with Yiannos Manoli and Matthias Keller of the University of Freiburg, Germany, are recognized leaders in

8 B. Hoefflinger

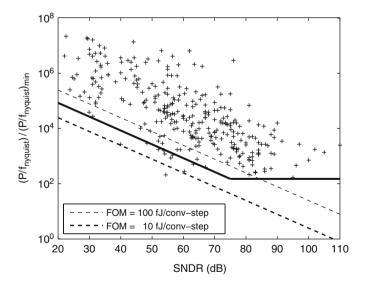

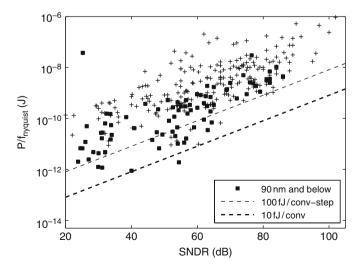

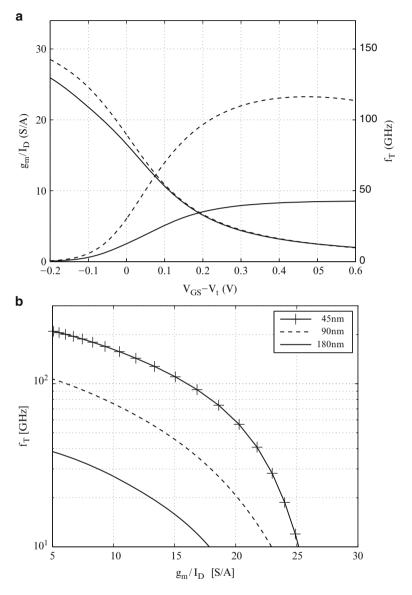

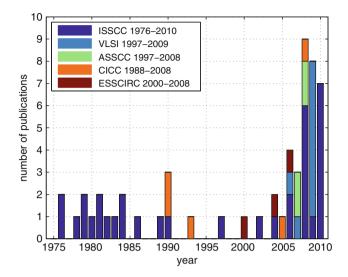

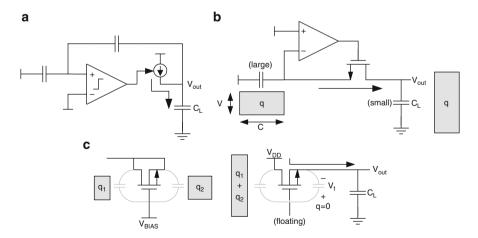

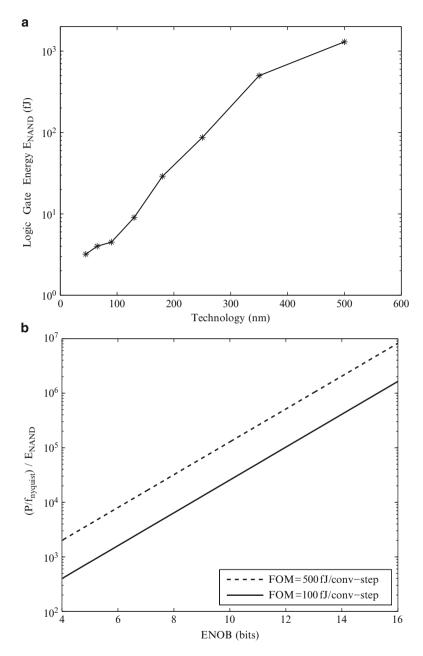

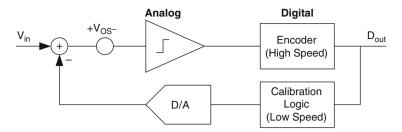

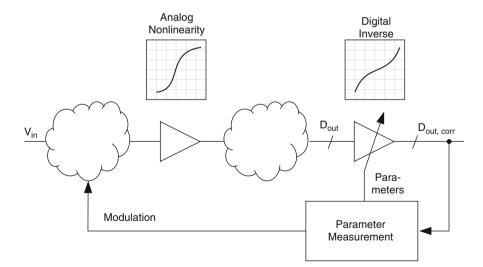

analog-digital converters, and they show in Chap. 4 that these converters have proceeded along their own, remarkable roadmap of energy per conversion and that there is great potential for future improvements in energy and speed using advanced, high-density CMOS technology nodes for digital-processing-based iteration and correction schemes at low voltages for precision conversion rather than traditional high-voltage, operational-amplifier-based converters.

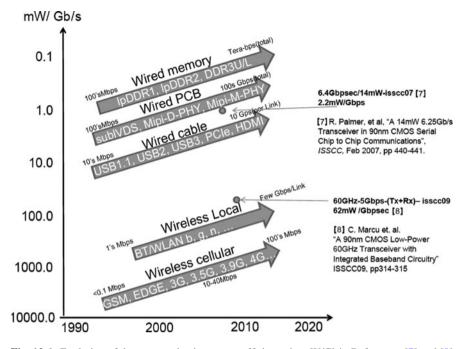

Interconnects, transmitters, and receivers are studied in Chap. 5, and we find that these communication functions are the most difficult to reduce in their energy requirements. Even today, they make up  $\sim 1/3$  of the total energy of chip systems, and even with a rigorous transition to low-voltage differential signaling as well as with 3D integration for shorter communication distances, the energy per bit will only be reduced by < 100 times in a decade (Fig. 1.4).

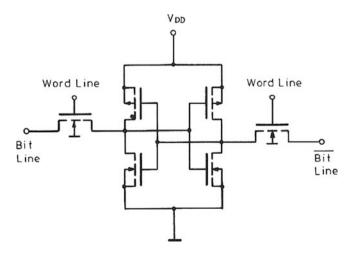

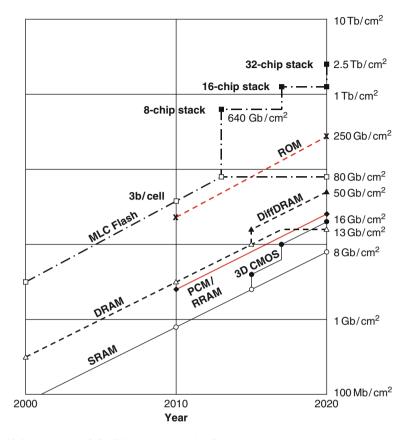

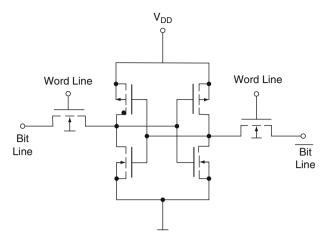

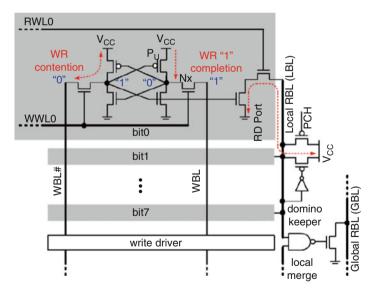

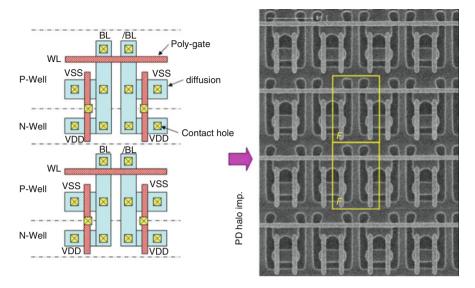

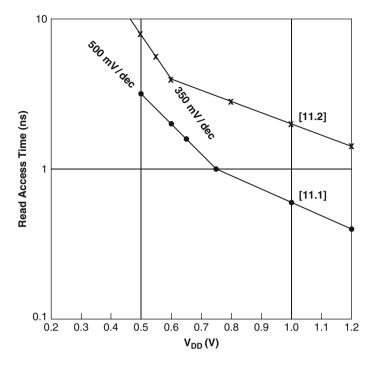

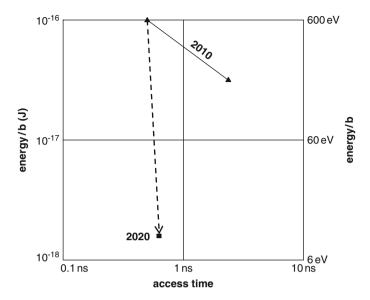

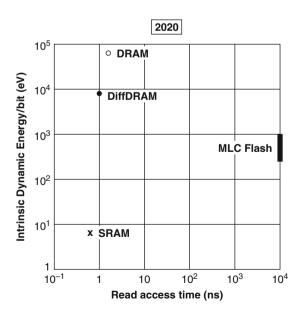

Memory energy is responsible for about another 1/3 of a chip-system's energy, and we will see in Chap. 11 that different memory types need different strategies for their advancement. The high-speed static CMOS random-access memory (SRAM) is best prepared for down-sizing both in footprint and in dynamic energy because of its differential *active* cell and differential sense amplifiers. It will also benefit fully from the 3D device-level integration of the fundamental four-transistor differential regenerator, so that it can reach a density of 16 Gbit/cm² by 2020 with a dynamic energy per bit of just 7 eV (Fig. 1.4). The density of a dynamic RAM (DRAM) is 5 times higher in 2010. However, DRAM can only be scaled to 22 nm and 13 Gbit/cm². A differential DRAM is proposed, which would enable a 2D density of 50 Gbit/cm² by 2020 and a read energy of 8,000 eV, eight times better than the best DRAM.

Figure 1.4 shows the development potential of the power efficiency of digital multipliers (their energy per operation) and SRAM as well as DRAM (dynamic energy per bit) over the decade 2010–2020. The remarkable advances are detailed in the corresponding chapters. All these functions reach or surpass the femtoelectronic mark or that of a neuron's synapse at  $10 \text{ fJ} = 6 \times 10^4 \text{ eV}$  per operation (per bit).

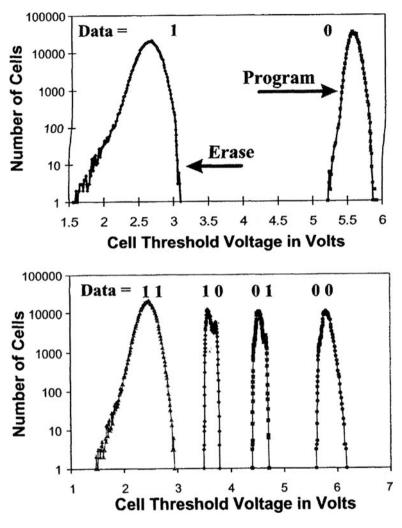

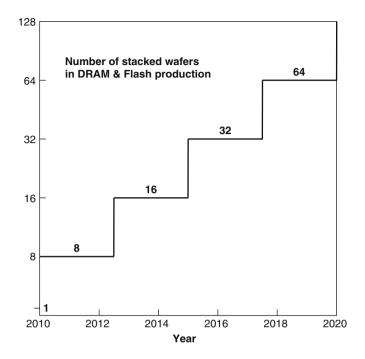

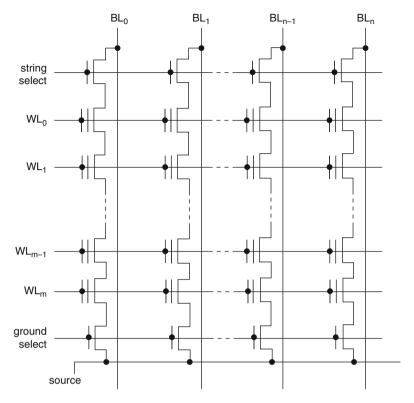

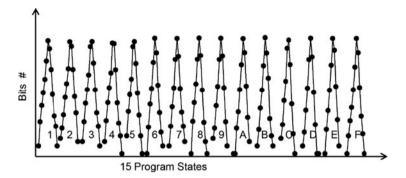

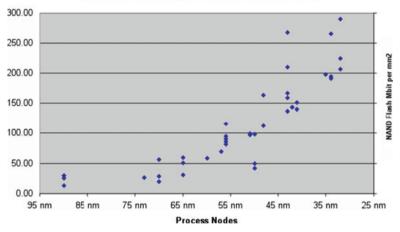

Multilevel flash memories, the large-scale leaders among nonvolatile memories, have made impressive progress since their first realization 1985. They are heading towards a minimum of 500 eV/bit, but again with a scaling limit at 22 nm (3 bits per cell) or 16 nm (2 bits per cell). These nonvolatile memories have seen the largest development effort on 3D integration into chip stacks of up to 128 chips, producing densities of many terabits per square centimeter. These *solid-state drives* (SSDs) are displacing magnetic-disk memories. Among the alternative styles of nonvolatile RAMs, phase-change (PCM) and resistive (RRAM) memories are progressing towards 20 Gbit/cm<sup>2</sup>. More aggressive tokens for a nonvolatile bit, for example the spin of an electron, continue to be burdened by energy- and space-hungry write-and-read transistor circuitry. Single-electron wells with Coulomb confinement may become the elements for a quantum-CCD (charge-coupled device) memory.

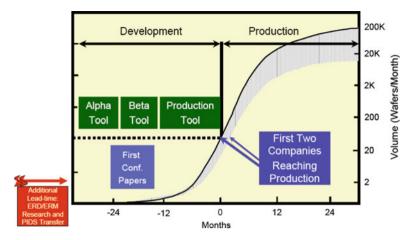

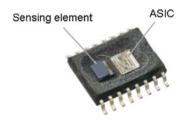

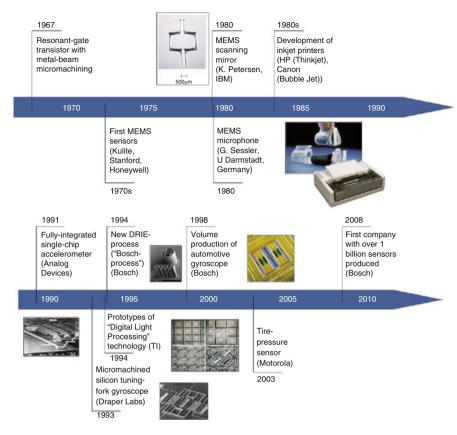

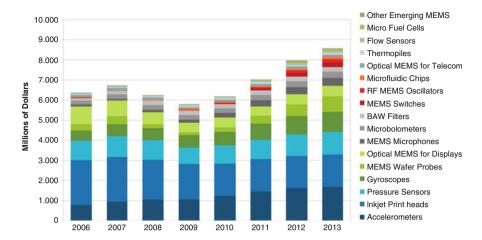

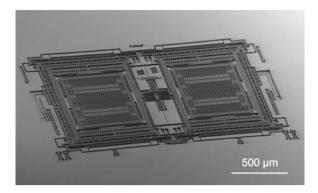

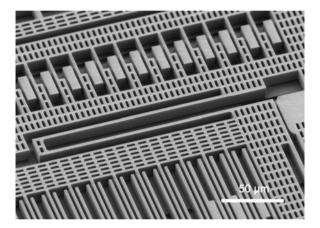

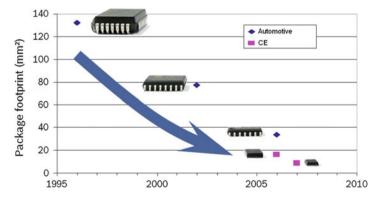

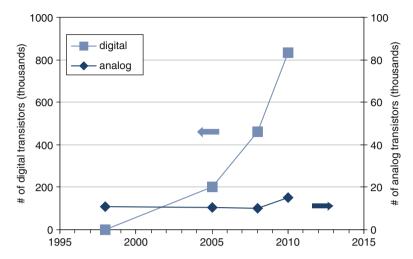

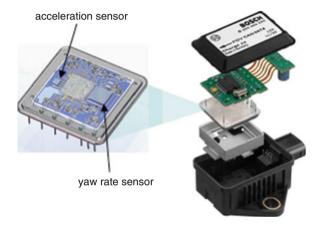

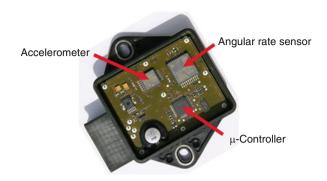

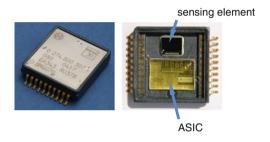

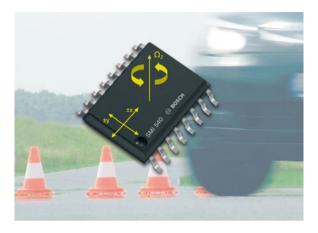

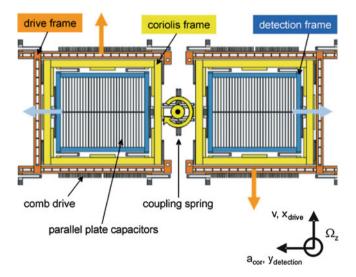

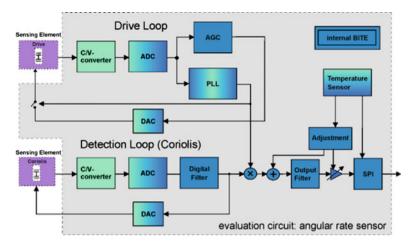

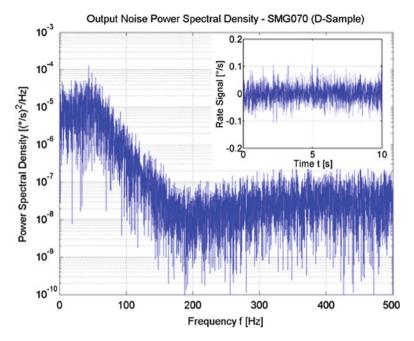

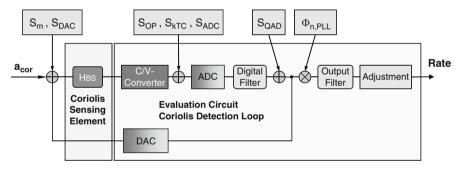

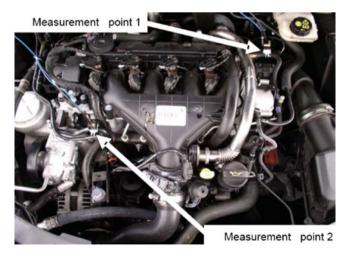

Regarding the variety of sensors, Jiri Marek and Udo-Martin Gómez of Robert Bosch GmbH, Germany, world leaders in micro-electro-mechanical systems (MEMS) for automotive applications, present, in Chap. 14, a comprehensive and quantitative overview of how much it takes in creative and extreme quality-

conscious development to put >1 billion safety-critical electromechanical sensing systems on the road. Tiny 3D mechanical structures combined with calibration and processing chips are applied for the realization of new sensing systems as well as for optimizing energy and manufacturing costs. These sensing systems are now expanding into many, particularly portable, consumer products.

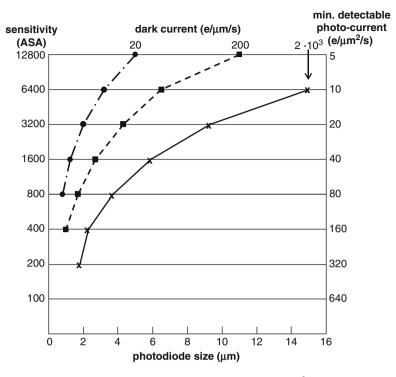

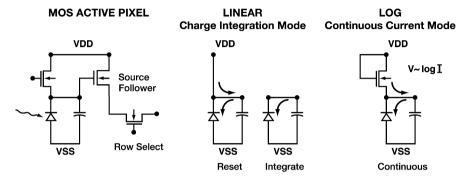

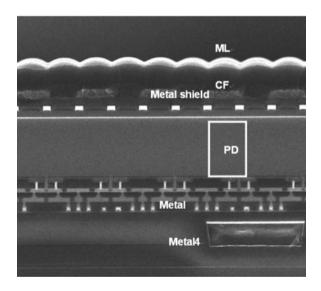

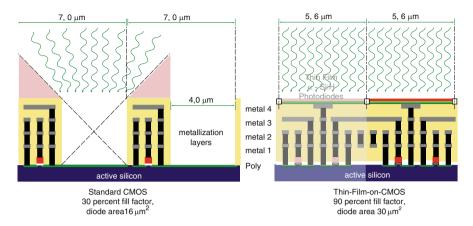

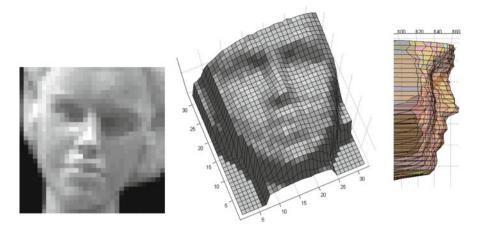

The other very important, highly integrated sensor systems are those for imaging and video. These are discussed in Chap. 15 with respect to selected topics such as sensitivity and pixel dark current, resolution and lens aperture, 3D integration or backside illumination for high sensitivity, eye-like high dynamic range, and 3D imaging. The performance of vision sensors is the first level in the complex and endlessly challenging system of intelligent vision and performance- and bandwidth-efficient video.

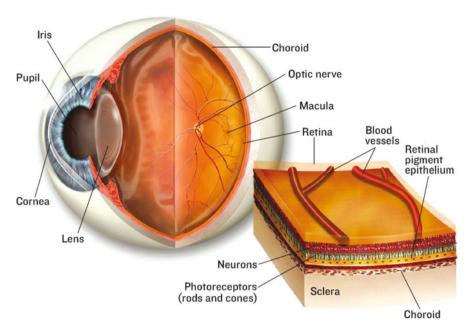

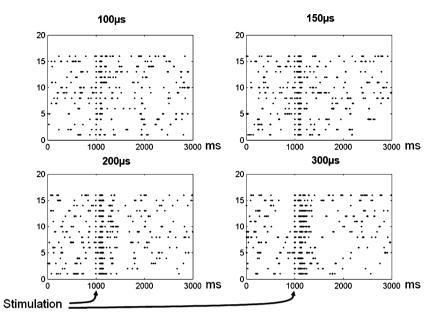

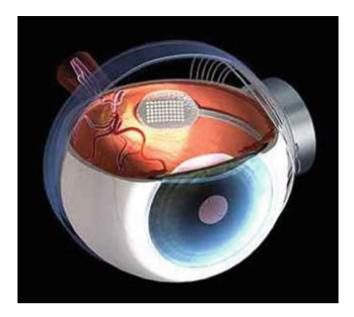

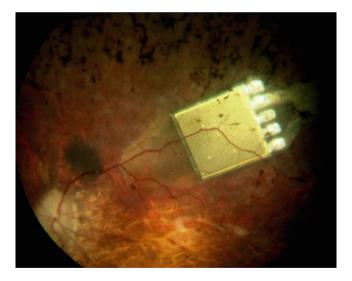

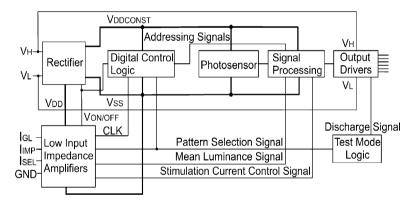

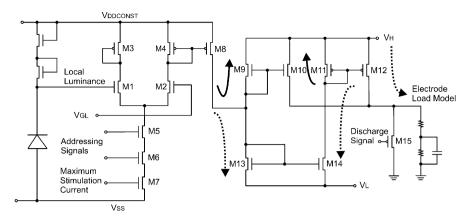

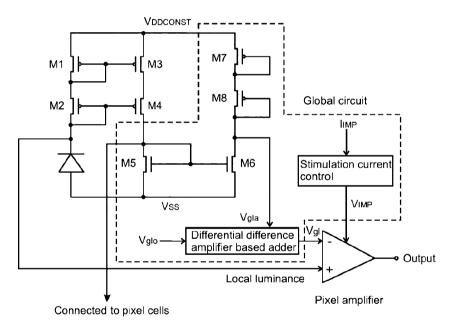

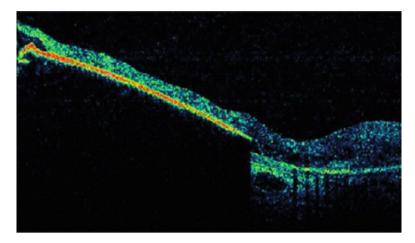

Very demanding vision specialties are retinal implants for blind people. Albrecht Rothermel, the chip specialist in one of the world-leading consortia for such implants, gives a balanced overview of the global status in 2010 in Chap. 17. He describes in a holistic spirit all aspects, including chip design, physiology, surgery, and training with patients; he further outlines what we can expect by 2020.

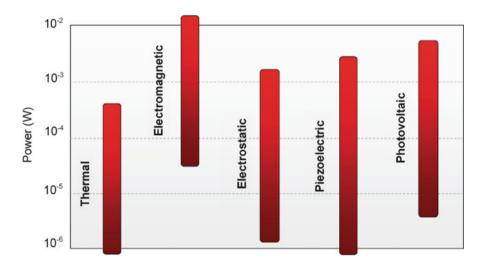

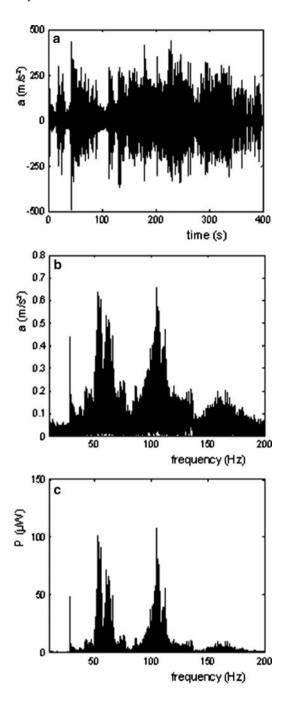

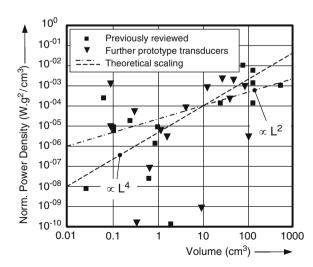

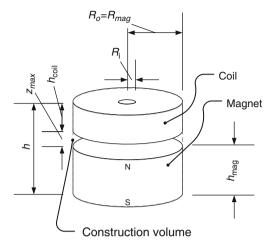

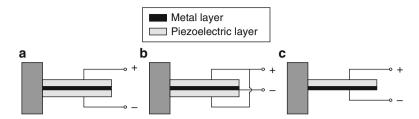

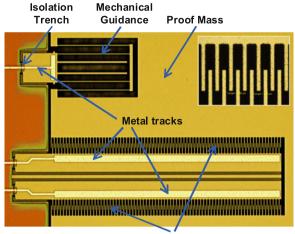

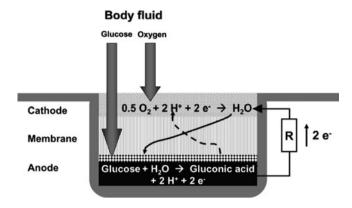

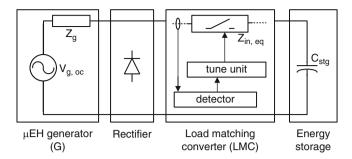

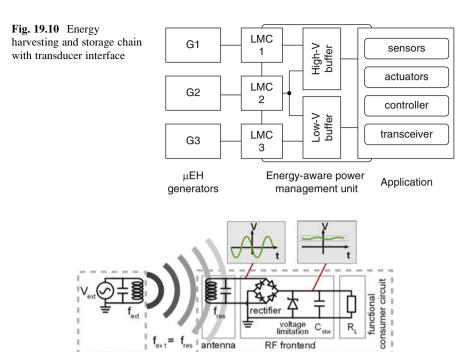

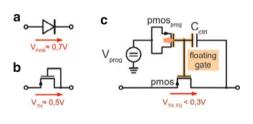

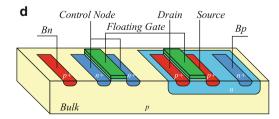

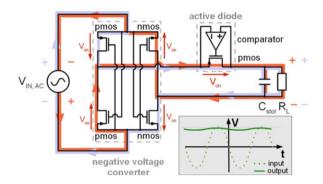

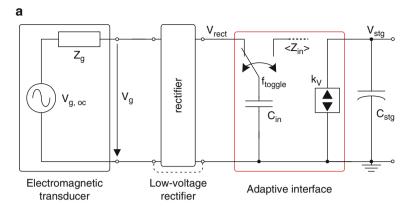

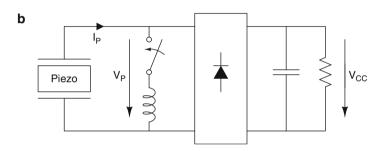

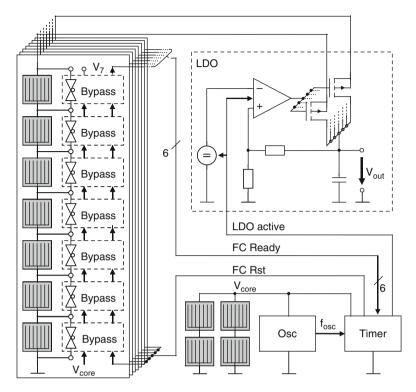

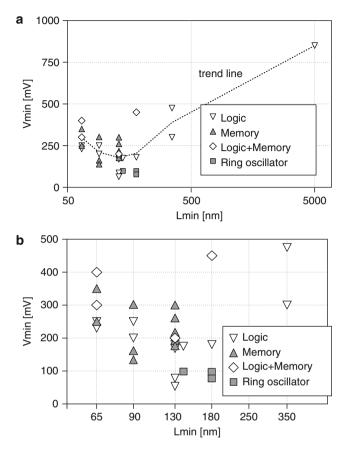

Implants are the exemplary type of chips for which energy is the dominant issue. How can we possibly produce energy on-chip or *harvest* energy on the chip or from its environment? One of the leading institutes in the field of energy harvesting is IMTEK, the Institute for Microsystems Technology in Freiburg, in cooperation with IMIT, Germany. Yiannos Manoli and his team present an exceptional tutorial, assessing the state-of-the art and highlighting future developments of such sources as motion, vibration, temperature differences, light, biofuel, and fuel cells. These sources and transducers operate in ultralow-voltage systems, and the authors show in Fig. 19.17 that, as of 2010, minimum supply voltages have been realized at L=130 nm, while voltages had to be higher at shorter gate lengths, results confirming – as in our introductory Fig. 1.1 – that, energy-wise, *shorter is no longer better*.

# 1.4 What Are the Requirements for New Chip Products and How Can We Meet Them?

After the assessment of Si technology and circuit capabilities and limits, we reflect these against the requirements in the major market categories for nanoelectronics (Table 1.2).

**Table 1.2** Areas of applications and the chapters in which they are treated

| Topic                              | Chapter |

|------------------------------------|---------|

| Overview and markets               | 6       |

| Superprocessors and supercomputers | 10      |

| Wireless and mobile companions     | 12, 13  |

| Automotive applications            | 14      |

| Medical implants                   | 17      |

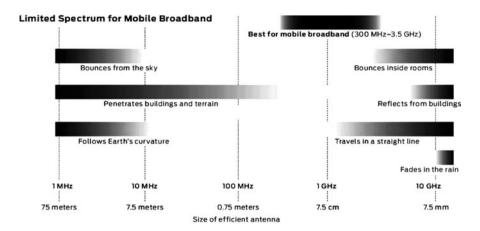

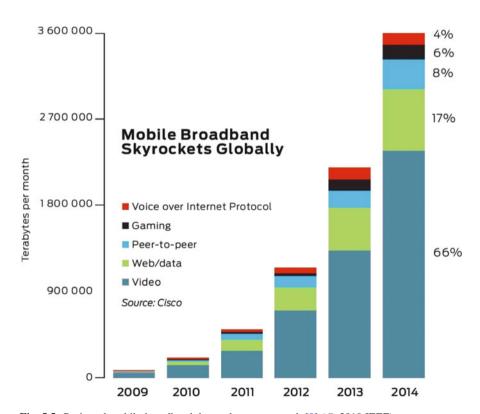

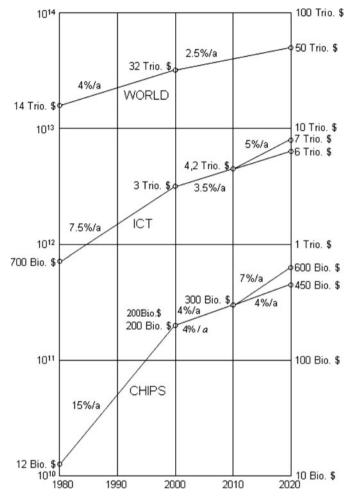

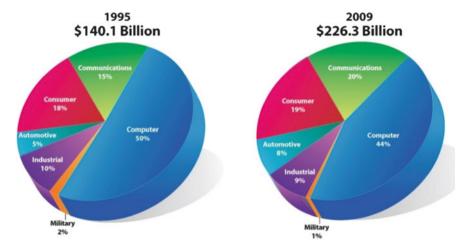

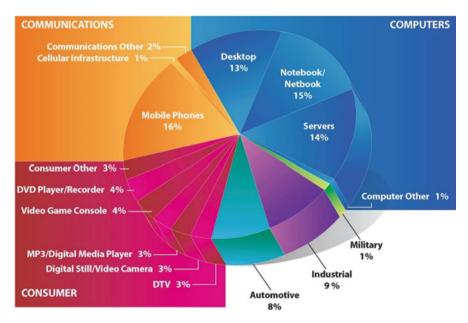

The overview in Chap. 6 tells us that the semiconductor industry, with aggregate growth rates of 4–7% per year, advancing toward >450 billion US\$ by 2020, continues to be the technology driver for the information and communication economy. Communication, consumer, and automotive chip markets show growth rates above average. The perspective of

- Six billion mobile-phone subscribers,

- A computer tablet per student with free access to the world's libraries, and

- A carebot (personal robot) per family (in Asia)

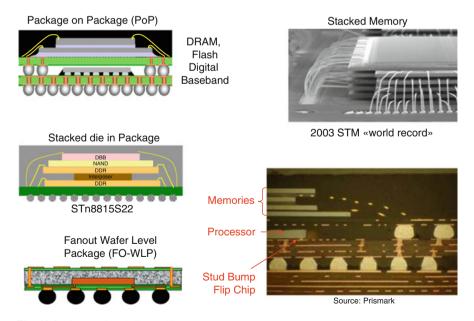

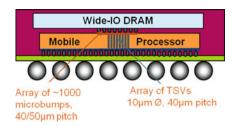

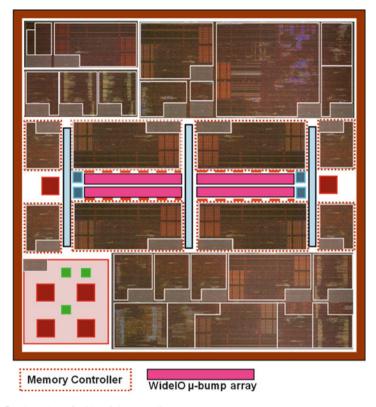

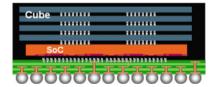

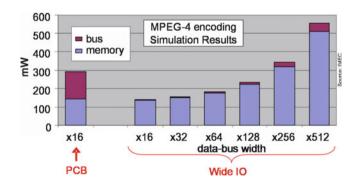

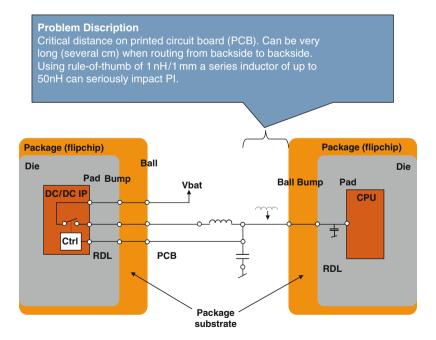

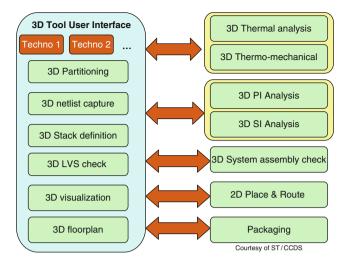

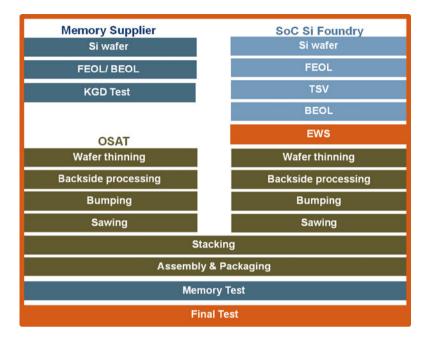

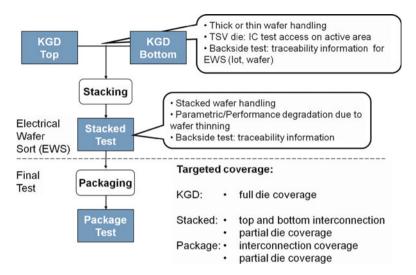

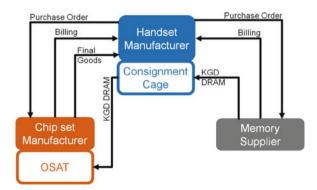

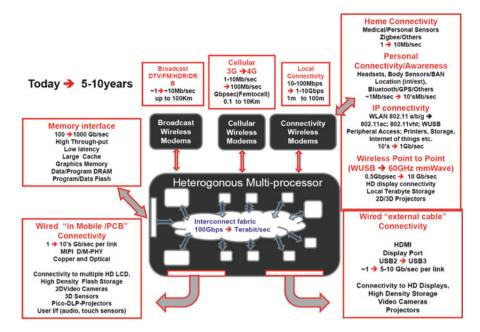

explains our emphasis on wireless mobile. Georg Kimmich, the system-on-chip product manager at ST Ericsson, describes, in Chap. 12, the remarkable progress of the 3D integration of heterogeneous chips, processors, memories, and transceivers, in close interaction with wide-bandwidth architectures, toward high-quality, cost-effective multimedia. In Chap. 13 Greg Delagi, Senior Vice-President for Wireless Systems at Texas Instruments, takes on the full perspective of the personal mobile companion of 2020:

- 3D imaging and display,

- Gesture interface,

- Integrated projection,

- Object and face recognition,

- Context awareness,

- Internet of things

- Brain-machine interface,

- Body-area network connection.

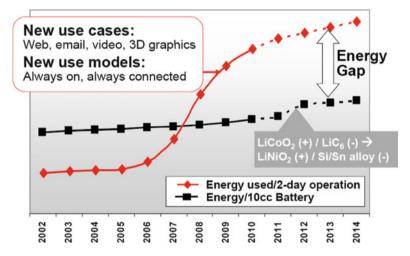

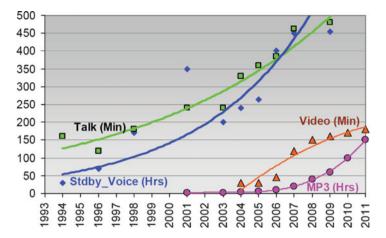

His chapter is the most explicit catalog of requirements on functional throughput, transceiver sensitivity, power, and bandwidth, and, throughout, a 1,000 times less energy per function, ultralow-voltage circuitry being the first thing to be promoted.

On the other side of the energy equation, he stresses the needed progress on energy harvesting. Considering the magnitude of the challenges, he asks for a "strong collaboration in research and development from universities, government agencies, and corporations" (see Sect. 1.6 and Chap. 22).

# 1.5 Which Radical Femtoelectronic Solutions Should We Seek for Intelligent Computing?

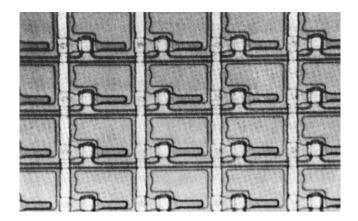

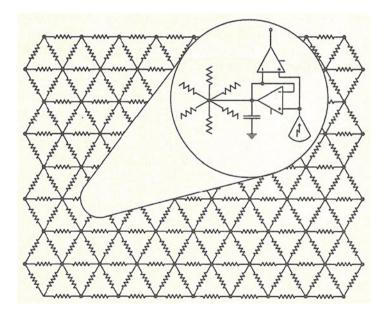

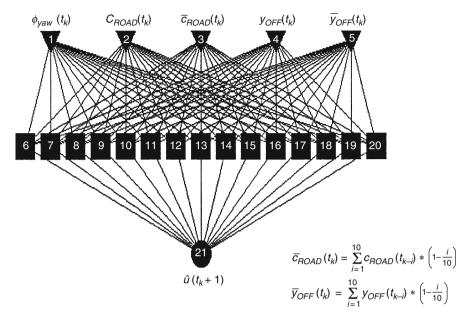

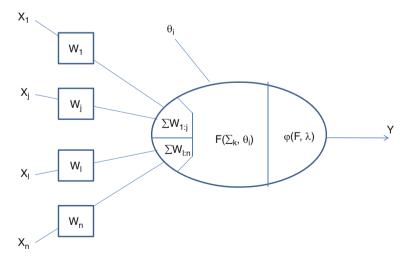

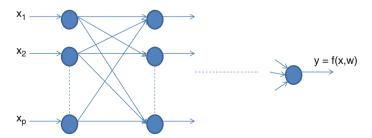

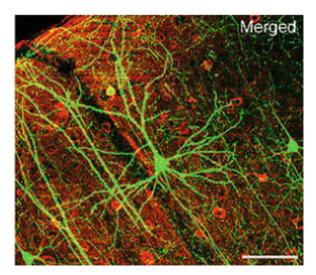

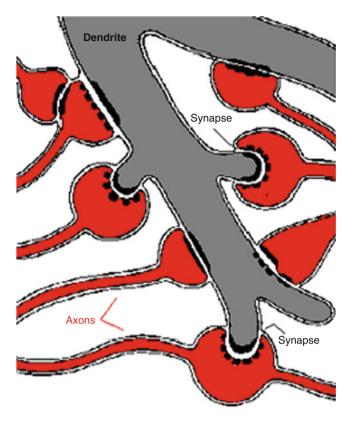

As alternatives to traditional computing architectures with processor, instructionand data-memory, artificial neural networks (ANNs) saw about a dozen years of intense research between 1988 and 2000, as often, a bit too early to have a broad, disruptive impact. Systems with a large number of inputs and with tasks of making decisions or recognizing patterns on the basis of rules, learning, and knowledge can be realized with these networks at speeds and energy levels unmatched by other architectures. Their final success is more likely now, because integrated electronic *neurons* are becoming effective on all counts at Si technology nodes <100 nm and because their fundamental 3D architecture can finally be realized with the large-scale introduction of 3D chip integration. Digital neural networks and silicon brains are treated in Chaps. 16 and 18, respectively.

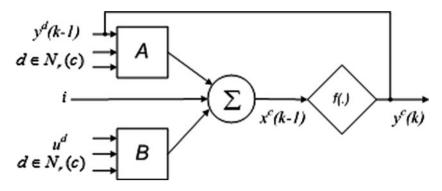

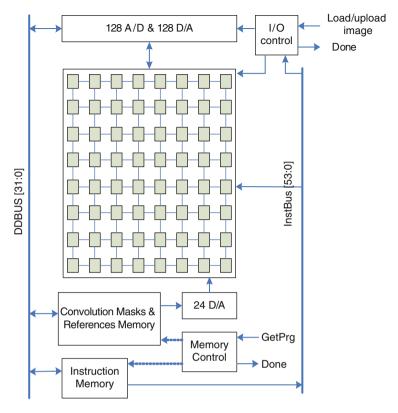

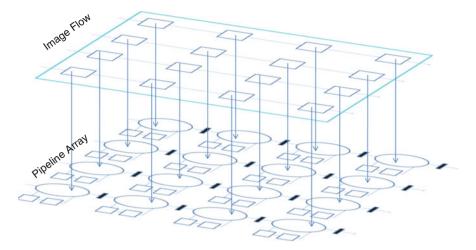

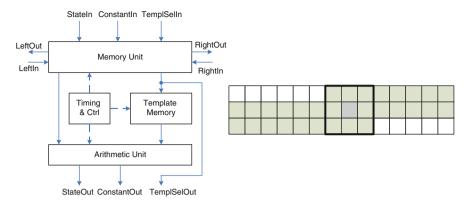

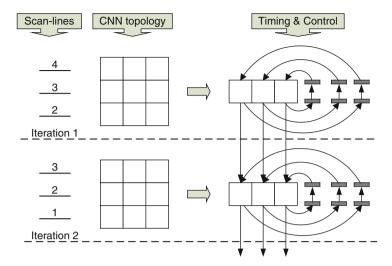

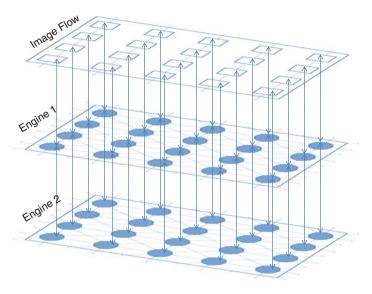

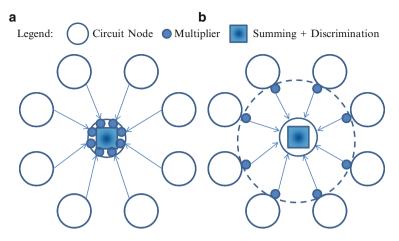

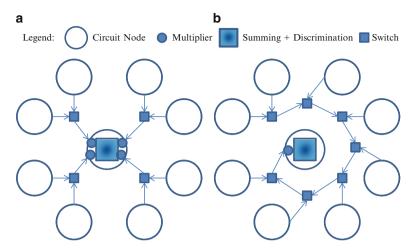

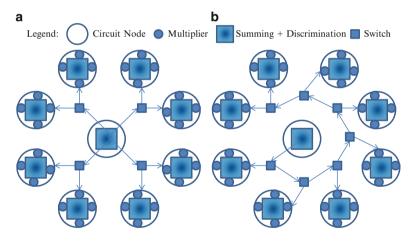

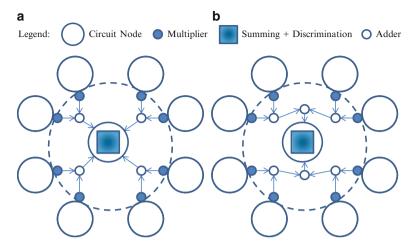

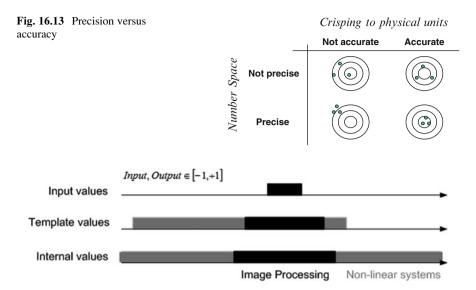

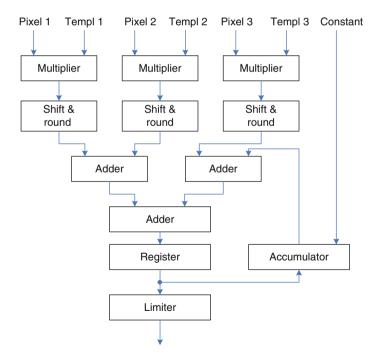

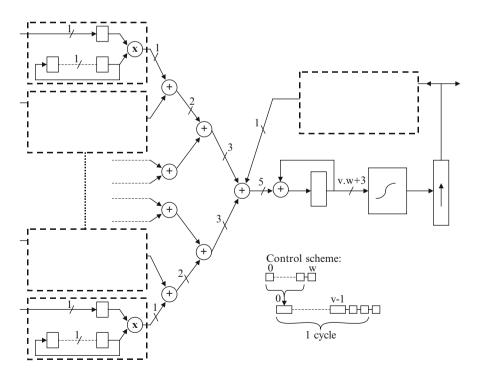

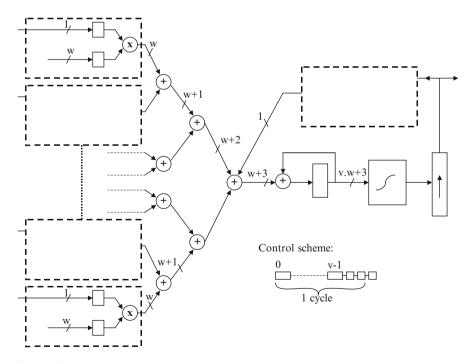

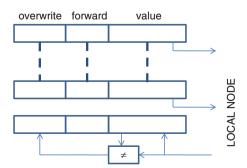

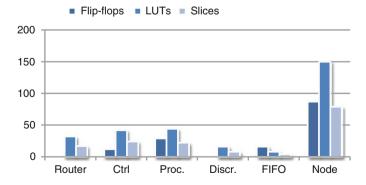

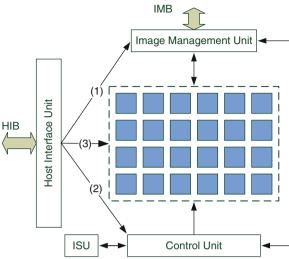

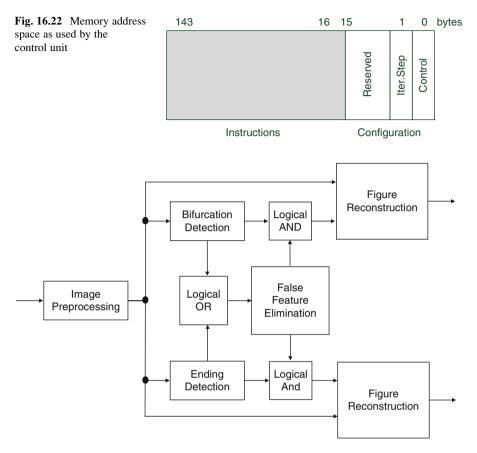

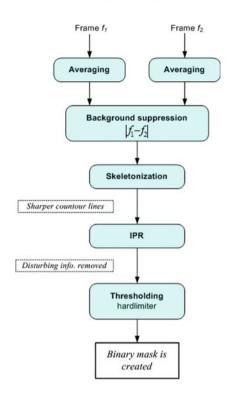

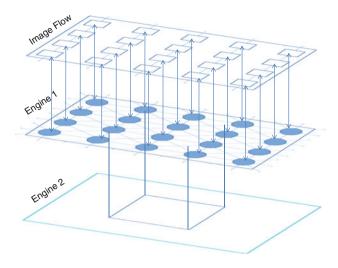

Ben Spaanenburg of Lund University, Sweden, has had a distinguished career in high-level chip design and cellular neural networks (CNNs). He and his coworker Suleiman Malki present a concise tutorial on working CNN chips and chip systems, both analog and digital. They describe new digital neuroprocessors for *vision-in-the-loop* new media tasks, from software, through scalable architecture, to digital-neuron design.

These CNNs are based on the extensively studied multilayer perceptron, which has become a quasi standard. By contrast, really radical research programs were launched in 2008 on *silicon brains*; on the one hand because of the availability of ultralarge-scale nano-CMOS and 3D chip integration, but actually with the intention of building general-purpose, biomorphic chip systems with the brain's complexity of  $10^{11}$  neurons and  $10^{14}$  synapses (Chap. 18).

# 1.6 What Are the Challenges for the Femtoelectronics Ecosystem of Education, Research, and Business?

The broad front along which chips can be advanced raises questions concerning all kinds of resources: the energy crisis (Chap. 20), the extreme-technology industry (Chap. 21), and education and research (Chap. 22).

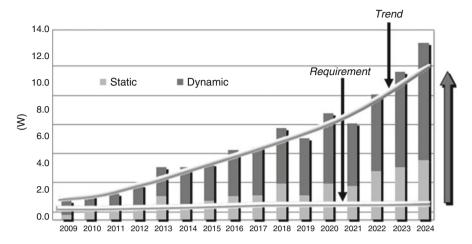

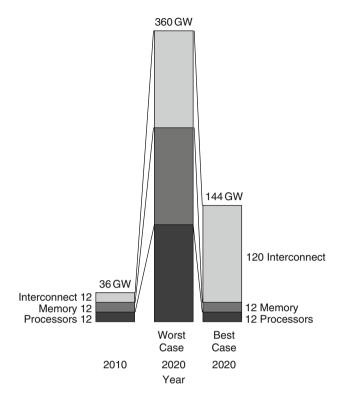

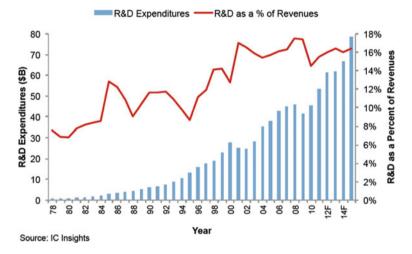

The globally installed electric power in 2010 is ~2 TW (2  $\times$  10<sup>12</sup> W). Information and communication technology (ICT), operated by electronic chips, is estimated to need >20% of the world's electric power. In Chap. 20, we look just at the needs of data centers, those server farms with 36 million servers in 2010, the processing backbone of the internet. They require ~36 GW, 10% of the total electric power installed in Europe. These data centers need and are expected to increase their performance 1,000-fold within a decade. This is obviously incompatible with the electric power available, unless this performance increase is achieved with, hopefully, a 1,000-fold improvement in power efficiency per function, which is synonymous with a 1,000-fold reduction in energy per function, the magic factor throughout this book. We also note in Chap. 20 that energy in a gigafab makes up >80% of the cost of a fully processed Si wafer. This leads us to Chap. 21 on the chip industry as "the extreme-technology industry", marked by an investment rate >15% as well as an R&D rate >15% of revenues, twice as high as the R&D rate of the top *pharmaceuticals* company in the Organisation for Economic Co-operation and Development (OECD) list of high-tech industries.

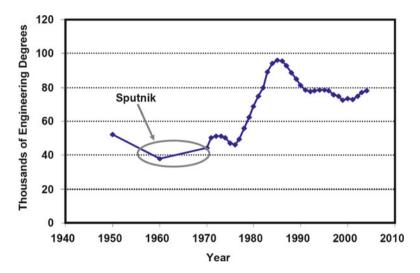

Naturally, these unique rates of progress can only be achieved with a unique interest in and unique investments in highly skilled manpower at all levels from kindergarten to retirement (Chap. 22). The concerns about the ecosystem of

education, research, industry, government, and the public are global. However, no wave, like the one triggered by *Sputnik* in the 1960s or that in the 1980s is in sight as of 2010.

After the world financial crisis of 2008–2009, with limited global financial and energy resources, a clear, requirements-driven research strategy should be established. For chips, as consistently stated throughout this book, the strategy should be *sustainable nanoelectronics towards femtojoule electronics*, with the key applications *educational tools*, *health and care*, *communication*, and *safe mobility*.

# 1.7 How Does the 2020 World Benefit from Femtoelectronic Chips?

The refocusing from a nanometer to a femtojoule strategy for nanoelectronics makes possible functionally powerful, energy-conscious chip systems serving the global base of six billion potential customers. As stated in Chap. 23, many of these pervasive chip innovations support health and safety in public, in private, and on the shop floor, so they should be accompanied, from the outset, by qualification and certification programs. Again, meeting the concerns of twenty-first century people, minimum-energy nanoelectronics can attract broad interest in the public, well beyond just the nanometer experts.

# **Chapter 2 From Microelectronics to Nanoelectronics**

**Bernd Hoefflinger**

**Abstract** We highlight key events in over 100 years of electronic amplifiers and their incorporation in computers and communication in order to appreciate the electron as man's most powerful token of information. We recognize that it has taken about 25 years or almost a generation for inventions to make it into new products, and that, within these periods, it still took major campaigns, like the Sputnik effect or what we shall call 10× programs, to achieve major technology steps. From Lilienfeld's invention 1926 of the solid-state field-effect triode to its realization 1959 in Kahng's MOS field-effect transistor, it took 33 years, and this pivotal year also saw the first planar integrated silicon circuit as patented by Noyce. This birth of the integrated microchip launched the unparalleled exponential growth of microelectronics with many great milestones. Among these, we point out the 3D integration of CMOS transistors by Gibbons in 1979 and the related Japanese program on Future Electron Devices (FED). The 3D domain has finally arrived as a broad development since 2005. Consecutively, we mark the neural networks onchip of 1989 by Mead and others, now, 20 years later, a major project by DARPA. We highlight cooperatives like SRC and SEMATECH, their impact on progress and more recent nanoelectronic milestones until 2010.

# 2.1 1906: The Vacuum-Tube Amplifier

At the beginning of the twentieth century, the phenomenon of electricity (the charge and force of electrons) had received over 100 years of scientific and practical attention, and signals had been transmitted by electromagnetic waves, but their detection was as yet very limited, because signal levels were small and buried in noise. This changed forever when the vacuum-tube amplifier was invented in 1906

B. Hoefflinger  $(\boxtimes)$

Leonberger Strasse 5, 71063 Sindelfingen, Germany

e-mail: bhoefflinger@t-online.de

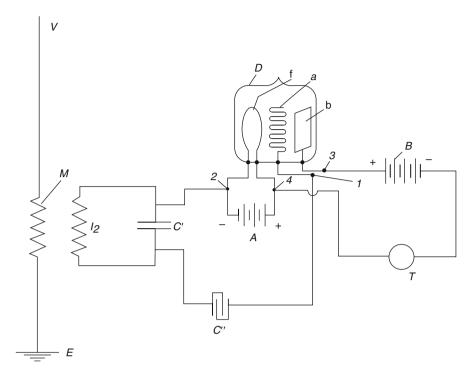

**Fig. 2.1** The vacuum-triode amplifier after De Forest 1907. In this field-effect triode, the electrodes are the heated cathode on the left, which we would call the source today, the grid in the center, which would be the gate, and the anode on the right, which we would call the drain (© USPTO)

by Robert von Lieben in Austria [1] and Lee De Forest in the USA [2]. Its predecessor was the vacuum-discharge diode, a two-terminal device consisting of a heated cathode electrode emitting thermionic electrons, which are then collected through a high electric field by another electrode, the anode, biased at a high voltage against the cathode. This two-terminal device acts as a rectifier, offering a large conductance in the described case of the anode being at a higher potential than the cathode, and zero conductance in the reverse case of the anode being at a potential lower than the cathode. The invention was the insertion of a potential barrier in the path of the electrons by placing a metal grid inside the tube and biasing it at a low potential with respect to the cathode (Fig. 2.1). The resulting electric field between cathode and anode would literally turn the electrons around. Fewer or no electrons at all would arrive at the anode, and the conductance between cathode and anode would be much smaller. A variation of the grid potential would produce an analogous variation (modulation) of the cathode-anode conductance. This threeterminal device, the vacuum triode, consisting of cathode, anode, and control grid, became the first electronic amplifier: It had a certain voltage gain  $A_V$ , because the grid-cathode input control voltage could be made much smaller than the cathode-anode voltage, and it had infinite current gain  $A_I$  at low rates of input

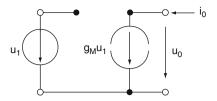

**Fig. 2.2** Equivalent circuit of an ideal amplifier (voltage-controlled current amplifier)

changes, because there was no current flow in the input between cathode and grid, while large currents and large current changes were effected in the output circuit between cathode and anode. As a consequence, the power gain  $A_VA_I$  approaches infinity.

It is worthwhile drawing the abstraction of this amplifier as a circuit diagram (Fig. 2.2), because inventors have by now spent over 100 years improving this amplifier, and they will spend another 100, even if the signal is not electrons. We see that the input port is an open circuit, and the output port is represented by a current source  $g_m V_{in}$  in parallel with an output resistance  $R_{out}$ .

The inventors of the vacuum-tube amplifiers were tinkerers. They based their patent applications on effects observed with their devices and achieved useful products within just a few years (1912).

10×: Long-range radio (World War I)

These amplifiers launched the radio age, and they triggered the speculative research on building controlled-conductance amplifying devices, which would replace the bulky vacuum tubes with their light-bulb-like lifetime problems.

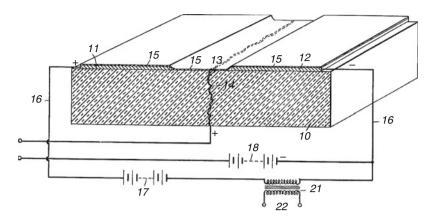

## 2.2 1926: The Three-Electrode Semiconductor Amplifier

The best solid-state analogue to the vacuum tube would be a crystal bar whose conductance could be varied over orders of magnitude by a control electrode. This is what the Austro-Hungarian—American physicist Julius Lilienfeld proposed in his 1926 patent application "Method and apparatus for controlling electric currents" [3]. He proposed copper sulfide as the semiconducting material and a capacitive control electrode (Fig. 2.3). This is literally a parallel-plate capacitor, in which the field from the control electrode would have an effect on the conductance along the semiconducting plate.

He did not report any practical results. However, since the discovery of the rectifying characteristics of lead sulfide by K.F. Braun in 1874, semiconductors had received widespread attention. However, it was not until 1938 that Rudolf Hilsch and Richard Pohl published a paper, "Control of electron currents with a three-electrode crystal and a model of a blocking layer" [4], based on results obtained with potassium bromide. Shockley wrote, in his article for the issue of the *IEEE Transactions on Electron Devices* commemorating the bicentennial of the United

Fig. 2.3 The field-effect triode proposed by Lilienfeld in 1926 (© USPTO)

States in 1976 [5], that he had this idea in December 1939: "It has occurred to me today that an amplifier using semi conductors rather than vacuum is in principle possible". Research continued during World War II on the semiconductor amplifier [6], but a critical effort began only after the war. As we shall see, it was not until 1959 that the Lilienfeld concept was finally reduced to practice.

#### 2.3 1947: The Transistor

One possible launch date of the Age of Microelectronics is certainly the invention of the transistor in 1947 [5]. Shockley himself described the events leading to the point-contact transistor as the *creative failure mechanism*, because the invention resulted from the failure to achieve the original goal, namely a field-effect transistor (FET) with an insulated gate in the style of the Lilienfeld patent. Nevertheless, this *failure*, implemented as Ge or Si bipolar junction transistors, dominated microelectronics into the 1980s, when it was finally overtaken by integrated circuits based on insulated-gate FETs, the realization of the Lilienfeld concept.

## 2.4 1959: The MOS Transistor and the Integrated Circuit

Shockley described the first working FET in 1952, which used a reverse-biased pn junction as the control gate, and junction FETs (JFETs) were then used in amplifiers, where a high input impedance was required. In fact, when I was charged in 1967 at Cornell University with converting the junior-year lab from vacuum tubes to transistors, I replaced the vacuum triodes in the General Radio bridges by junction FETs, and one of my students wrote in his lab report: "The field-effect transistor thinks that it is a tube".

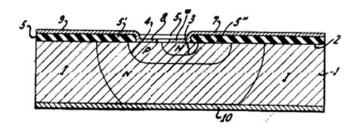

Fig. 2.4 The MOS transistor in Kahng's patent filed in 1960 (© USPTO)